複雑化するシステム制御を簡単に、LatticeのFPGA:3.3V I/Oサポートなどを強化(1/2 ページ)

Lattice Semiconductor(以下、Lattice)の日本法人であるラティスセミコンダクターは2022年5月31日、28nm FD-SOI(完全空乏型シリコン・オン・インシュレーター)プロセスを適用したFPGAプラットフォーム「Nexus」の第5弾製品として、「MachXO5-NX」を発表した。

Lattice Semiconductor(以下、Lattice)の日本法人であるラティスセミコンダクターは2022年5月31日、28nm FD-SOI(完全空乏型シリコン・オン・インシュレーター)プロセスを適用したFPGAプラットフォーム「Nexus」の第5弾製品として、「MachXO5-NX」を発表した。システムのモニタリングおよび制御に向けた機能を強化した製品で、サーバ、通信、産業機器、車載などの市場をターゲットとする。

ラティスセミコンダクターは、「MachXO5-NXは、最新のメモリを搭載したセキュアコントロールFPGAで、多くの3.3Vインタフェースをサポートする他、電力効率に優れた高信頼性のシステムの開発を容易にする」と述べる。さらに、セキュア制御に最適化したFPGAの投資を続けている「唯一のFPGAベンダーとなった」と強調した。

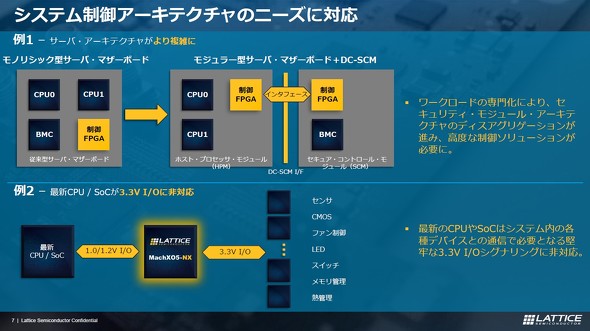

ラティスセミコンダクターは、システム制御のトレンドには3つのトレンドがあると説明する。システム制御アーキテクチャが複雑化していること、大量の3.3V I/Oインタフェースが必要とされていること、そして、シンプルなシステム設計と統合が不可欠になっていることだ。

MachXO5-NXは、こうしたニーズに対応すべく開発された製品だ。下図の例1のサーバアーキテクチャでは、BMC(Baseboard Management Cotroller)などをメインCPUボードから切り離し、CPUの世代交代を容易にするモジュラー型アーキテクチャへの移行が示されている。Latticeは既にこの分野に製品を提供している。下図例2では、最先端のプロセスを適用したCPUやSoC(System on Chip)と、レガシープロセスを適用するペリフェラルではI/Oインタフェースの動作電圧にギャップがあり、それを埋めるためにMachXO5-NXを使用できることを示している。

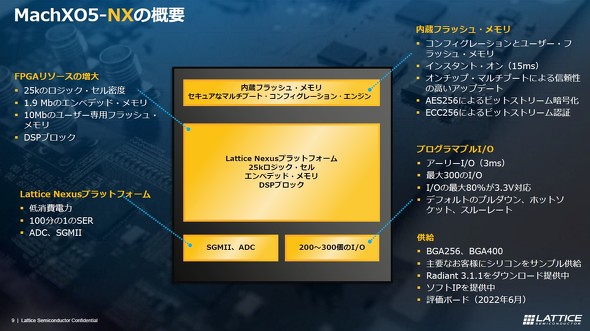

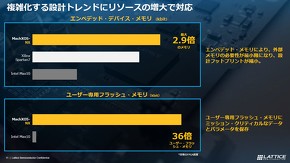

MachXO5-NXでは、複雑化する制御ロジックに対応するため、回路規模を25kロジックセルまで拡大。組み込みメモリの容量は2Mビット。最大10Mビットのユーザー専用フラッシュメモリを搭載しているので、ミッションクリティカルなデータやパラメータを保存できる。新しいアプリケーションに効率よく対応するために、DSPブロックも実装した。

インタフェースについては、アーリーI/Oコンフィギュレーション対応の汎用I/Oを最大300個搭載していて、そのうち80%が3.3Vをサポートする。

開発ツール「Radiant 3.1.1」やソフトウェアIP(Intellectual Property)を提供中で、2022年6月には評価ボードの提供も開始する。

ラティスセミコンダクターは「競合製品に比べ、MachXO5-NXは、シンプルなシステム設計に要求される多くの機能を備えている」と述べる。特に3.3Vインタフェースに関しては「ホットソケット、プログラマブルスルーレート、プルダウン、3ミリ秒で起動するアーリーI/Oを全てサポートする、堅ろうな3.3Vインタフェース」であると述べ、競合品はこうした堅ろうな仕組みを備えていないと主張した。

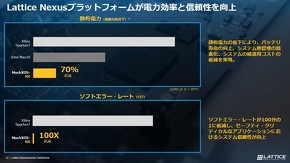

さらに、FD-SOIプロセスの採用とLatticeのデバイス設計により、MachXO5-NXは競合品に比べて消費電力を最大70%低減するという。これにより、システム熱管理を簡素化できる。

Copyright © ITmedia, Inc. All Rights Reserved.