米新興企業、光I/OチップレットでNVIDIAと協業へ:次世代のインターコネクト(1/2 ページ)

米国カリフォルニア州に拠点を置く新興企業Ayar Labsは、同社のチップ間光通信技術を中心としたエコシステムを構築するという。NVIDIAとの協業により、光I/O技術を適用した次世代アーキテクチャの開発に取り組んでいるところだ。

米国カリフォルニア州に拠点を置く新興企業Ayar Labsは、同社のチップ間光通信技術を中心としたエコシステムを構築するという。NVIDIAとの協業により、光I/O技術を適用した次世代アーキテクチャの開発に取り組んでいるところだ。

NVIDIAのデータセンタープロダクト部門担当チーフプラットフォームアーキテクトであるRob Ober氏は、報道向け発表資料の中で、「NVIDIAが過去10年の間に、コンピューティングを加速させてきたことにより、AI(人工知能)は数百万倍の高速化を実現することができた。この次に数百万倍の高速化を実現するためには、未来のAI/ML(機械学習)ワークロードやシステムアーキテクチャの帯域幅や電力、拡張要件などをサポートする上で、光I/Oのような高度な技術が新たに必要になるだろう」と述べている。

Ayar Labsのプレジデント兼CTO(最高技術責任者)であるMark Wade氏は、米国EE Timesのインタビューに応じ、「われわれは、これまでしばらくの間、NVIDIAと水面下で連携してきた。NVIDIAは、システムレベルの性能を毎年桁違いに向上させるべく取り組んできたが、今や、ファブリック性能がその大きな制限や妨げの要因となっているということが明らかになったとしている」と述べる。

「当社はこれまで長年にわたり、NVIDIAが提起した問題に対する取り組みを進めてきた。例えば、現時点の性能をはるかに上回る大規模なスケールアウトシステムを構築したい場合や、何千個ものGPUの論理的な接続を実現したい場合などは、全て同じニューラルネットワークの問題が関与しているため、スケールアウトファブリックの問題を解決する必要がある。NVIDIAはソリューションの方向性を、『物理学やフォトニクス、光学などの第一原理こそが、唯一の方法である』と定めており、われわれはそれに足並みをそろえてきた」(Wade氏)

NVIDIAは公式見解として、「AIモデルの接続数は2023年までに、100兆個以上(2021年比で600倍超)に達するだろう。このため現時点では、既存の銅配線プラットフォームの技術的性能を超えるとみられている」と述べている。Ayar Labsは、「当社のチップ間光通信技術は、帯域幅密度を銅配線に比べて1000倍に高めると同時に、電力量とレイテンシを10分の1に低減することが可能だ」と主張する。

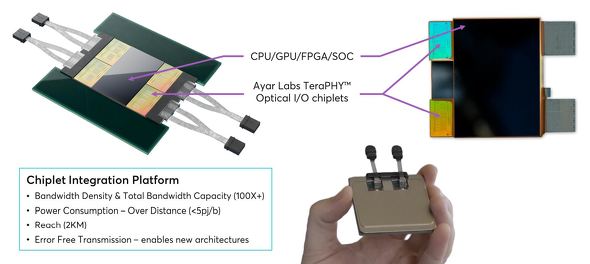

Ayar Labsは2015年に、米国マサチューセッツ工科大学(MIT:Massachusetts Institute of Technology)と、米国コロラド大学ボルダー校(University of Colorado Boulder)、カリフォルニア大学バークレー校(University of California, Berkeley)からのスピンアウト企業として設立され、光I/O技術の開発に取り組んできた。同社のチップレット「TeraPHY」は、ホストSoC(System on Chip)に隣接して配置され、光ファイバー経由で高帯域幅かつ高速、低消費電力のチップ間光通信を実現することができる。

Wade氏は、「われわれは何世代にもわたり、レクチル当たりのコンピューティング性能を拡張し続けてきた。しかし同時に、I/O帯域幅に関しては、2010年の時点で既に、後れを取らないよう必死についていくというような状況だった。このような帯域幅の制限を回避していく上で、電気I/O技術はどこまで対応できるのだろうか」と述べる。

この問題は、例えばI/Oに必要な電力量や、演算装置ごとに必要とされる帯域幅の量など、さまざまな次元において明らかになっている。電気的結合でリタイマーが必要とされるようになり、それに伴いシステムレベルのコストや複雑性が増大している。

Ayar Labsの技術は、こうした問題に対応するために開発された。同社は、光I/OチップレットをGlobalFoundriesで製造し、ダイを顧客向けに出荷する。そこで最新のチップレットインターポーザー技術を適用し、モジュール上のホストSoCに隣接してフリップチップ実装される。Ayar LabsのTeraPHYチップレットは、電気を光に変換するので、光ファイバーを使ってチップ間でデータを送受信することが可能だ。

Ayar Labsは現在、ホストSoCと光チップレットの間で電気インタフェースを使用している。これは2018年に、国防総省国防高等研究事業局(DARPA)のPIPESプロジェクトの一環として、Intelと共同開発したものだ。しかし、同社はいずれ、チップレット間の通信標準規格であるUCIe(Universal Chiplet Interconnect Express)とCXL(Compute Express Link)の両方の互換性を実現する予定だとしている。

Wade氏は、「われわれは、UCIe規格が、さまざまなソリューションを集結させていくための強力なけん引要素になるとみて、非常に興奮している。全てのチップレットメーカーが、現在この問題に直面しているところだ。どのメーカーも、自社の製品ロードマップを数百種類もの異なるSKU(Stock Keeping Unit/実在庫品番数)に断片化させたいとは思わないだろう。UCIeによってこの問題への対応が進みつつあることを、とてもうれしく思う」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.