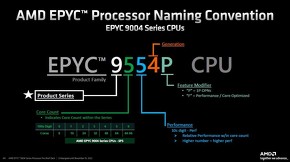

AMD、サーバ向け高性能プロセッサ「第4世代EPYC」の第1弾を発表:福田昭のデバイス通信(371)(1/2 ページ)

AMDは2022年11月10日(米国時間)に米国カリフォルニア州サンフランシスコで新製品発表会「together we advance_data centers」を開催し、サーバ向けプロセッサの新製品「EPYC 9004シリーズ」の販売を開始した。

最新CPUコア「Zen4」を最大で96個搭載

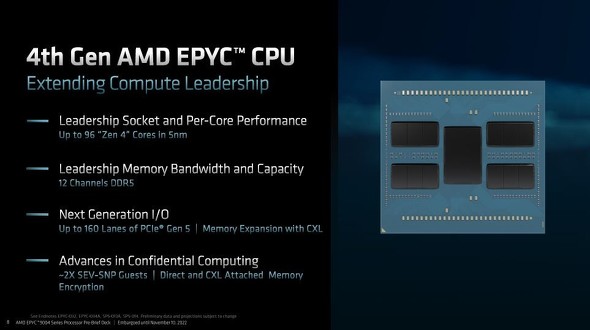

AMDは2022年11月10日(米国時間)に米国カリフォルニア州サンフランシスコで新製品発表会「together we advance_data centers」を開催し、サーバ向けプロセッサの新製品「EPYC 9004シリーズ」の販売を開始した。x86互換のCPUコア「Zen」シリーズの第4世代である最新のCPUコア「Zen4」を搭載する。Zen4を搭載するサーバ向けプロセッサ「第4世代(4th Gen)EPYC」では、最初の製品となる。なお「EPYC 9004シリーズ」の開発コード名は「Genoa(ジェノア)」である。

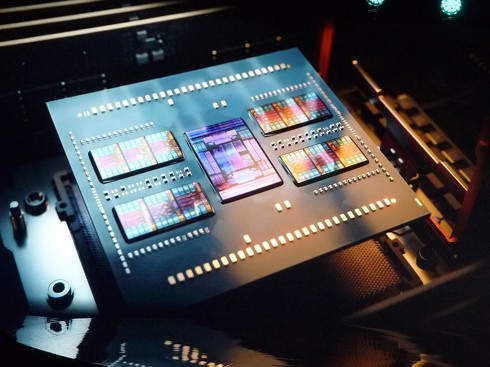

「第4世代(4th Gen )EPYC(「EPYC 9004シリーズ」)」の外観(パッケージに封止する前の状態)。樹脂基板(パッケージ基板)に複数のミニダイを載せた「チップレット」構成を採用している。2022年11月10日(米国時間)に新製品発表会「together we advance_data centers」で筆者が撮影したもの[クリックで拡大]

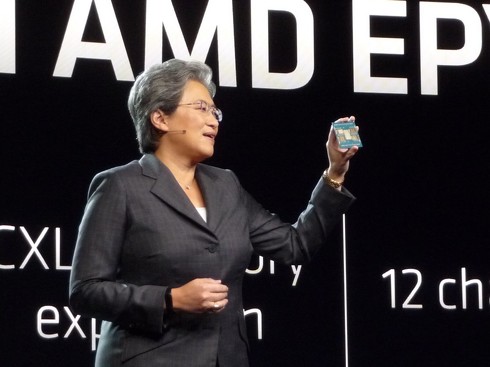

発表会のキーノート講演で「第4世代(4th Gen )EPYC(「EPYC 9004シリーズ」)」のパッケージ基板を掲げるAMDのチェア兼CEOを務めるリサ・スー(Lisa Su)氏。新製品発表会「together we advance_data centers」で筆者が撮影したもの[クリックで拡大]

「EPYC 9004シリーズ」の実装形態は、樹脂基板にZen4コア内蔵ミニダイ(「CCD」と呼称)と入出力(IO)ミニダイを並べたチップレット構成である。第2世代のEPYCからAMDが採用してきた実装形態だ。Zen4コア内蔵ミニダイは8個のZen4コアを内蔵しており、最大で12枚のミニダイを樹脂基板に搭載できる。すなわち最大構成は96コアとなる。第3世代のEPYCが最大で64コアだったので、搭載可能なコア数は1.5倍と大きく増加した。

Zen4コア内蔵ミニダイは5nm技術、入出力ミニダイは6nm技術で製造した。樹脂基板の大きさは72mm×75.4mmである。ミニダイ(CCD)のシリコン面積は3.84mm2とかなり小さい。

外部メモリインタフェースはDDR5 DRAMモジュールである。インタフェースのチャンネル数は12チャンネルとかなり多い。1チャンネルに接続可能なDRAMモジュール(DIMM)は最大で2枚。入出力インタフェースはPCIe Gen5インタフェースである。レーン数は最大で160レーンとこれもかなり多い。

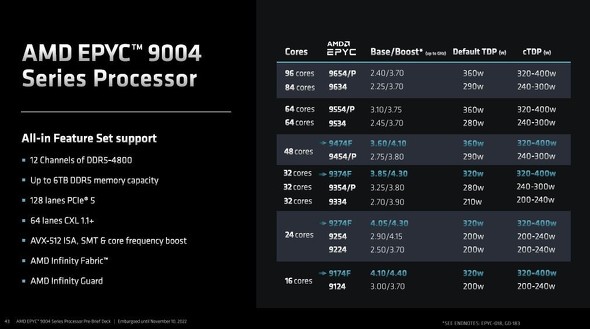

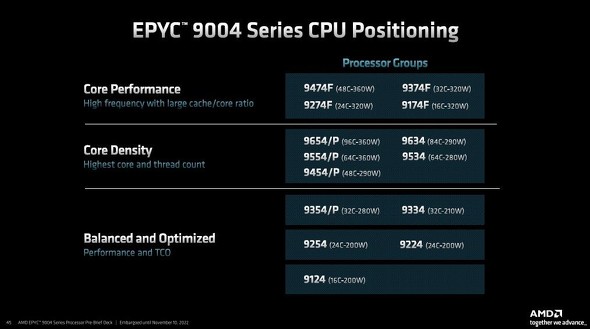

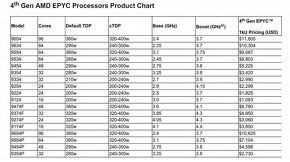

CPUコア数と動作周波数の異なる18品種を用意

「EPYC 9004シリーズ」では、CPUコア数や動作周波数、許容電力などの違いによって18品種を用意した。CPUコア数の最小構成は16コア、最大構成は前述の通り96コアである。18品種は特性の違いから、大きく3つに分かれる。動作周波数の最大化を優先したグループ、コア数の最大化を優先したグループ、価格を低めに抑えたグループ、である。

Copyright © ITmedia, Inc. All Rights Reserved.