半導体の設計、今後は「マルチフィジックス」解析が鍵に:複雑化するチップ設計に対応(1/2 ページ)

先端プロセスノードへの移行や、チップレット、3D(3次元) ICなどの技術が台頭する中、シミュレーションの世界にはどのような変化が起きているのか。Ansysの半導体・エレクトロニクス・光学ビジネス担当ゼネラルマネジャー、John Lee氏に話を聞いた。

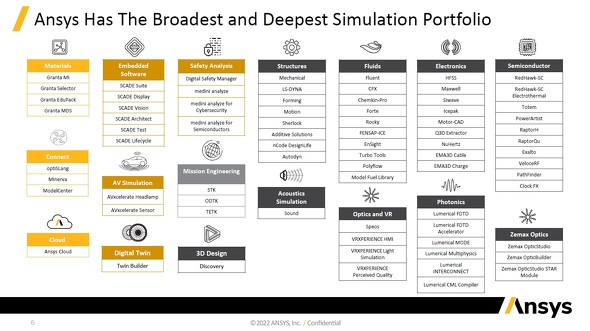

シミュレーションソフトウェアベンダーの大手であるAnsysは、構造や流体のみならず、電磁界のシミュレーションでも多くの実績を持っている。先端プロセスノードへの移行や、チップレット、3D(3次元) ICなどの技術が台頭する中、シミュレーションの世界にはどのような変化が起きているのか。Ansysの半導体・エレクトロニクス・光学ビジネス担当ゼネラルマネジャー、John Lee氏に話を聞いた。

複雑化の一途をたどるチップ設計

――現在、どのような半導体技術に注目していますか。

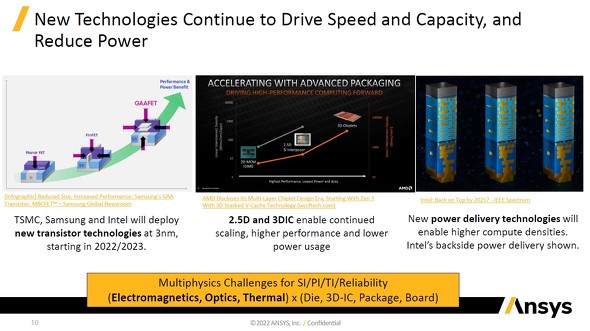

John Lee氏 最新のトランジスタ技術に注目している。その一つがGAA(Gate All Around)トランジスタ構造だ。TSMCやSamsung Electronics、Intelなど大手ファウンドリーは全てGAAをロードマップに組み込んでいる。主流になりつつある2.5D/3D ICや、Intelなどが開発しているロジックデバイスの裏面電源供給技術なども注目に値する技術だ。

――こうしたトレンドを踏まえ、シミュレーション分野では何が重要になっていますか。

Lee氏 新しい技術トレンドにより、チップはますます複雑になっている。これは、電気、磁場、熱、構造、流体といった複数の物理的要素(マルチフィジックス)をはじめ、シグナルインテグリティ(SI)やパワーインテグリティ(PI)、熱のインテグリティ、信頼性といったさまざまな要素も複雑化し、それらに対する要件を満たすことが難しくなっているということでもある。

そのため、特にマルチフィジックスに対応するソリューションの重要性が増している。

マルチフィジックスでの解析が重要になるのはチップ単体だけではない。パッケージ、引いては基板でも重要になる。シミュレーションツールは、マルチフィジックス対応だけでなく、チップレベル、パッケージレベル、ボードレベルのいずれにも対応できる“マルチスケール”であることも重要になる。

――マルチフィジックスやマルチスケールに対応するAnsysのソリューションには、どういった製品がありますか。

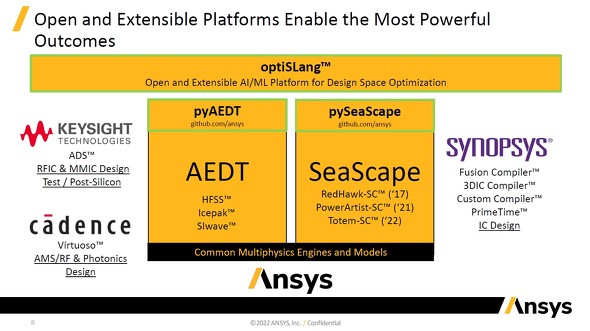

Lee氏 主にチップ設計向けプラットフォーム「SeaScape」や、パッケージおよびボード設計向けプラットフォーム「AEDT(Ansys Electronics Desktop)」がある。当社が10年以上にわたり提供してきた製品だ。これらのプラットフォームの特長は、さまざまな技術に対応できるオープン性と拡張性を備えていることだ。例えばAEDT上には、Ansysの3D電磁界解析ツールである「Ansys HFSS」を構築できる。SeaScape上には、SoCのパワーノイズや信頼性を評価する「RedHawk-SC」や、PIを解析する「Totem-SC」などを構築できる。

さらに、マルチフィジックスに対応すべく、EDAツールベンダーのSynopsysやCadence、高周波関連の設計/検証ツールを扱うKeysight Technologiesなどと密に協業している。

Copyright © ITmedia, Inc. All Rights Reserved.