CXL/UCIeから考える光インターコネクト技術:光伝送技術を知る(22) 光伝送技術の新しい潮流と動向(3)(3/4 ページ)

「ChatGPT」などのAI技術に後押しされ、データセンターは拡張の一途をたどるとされている。その際、光技術はどうあるべきなのか。今回は、チップレット間のインターコネクト技術である「CXL」や「UCIe」に着目し、ここから求められるであろう光インターコネクトの姿を探る。

チップレット/SiPとUCIe

Massive Node Compute Data Centerで使用されるIC技術はどのような物だろうか。先に述べたように、デナード則とムーアの法則に支えられてきたSoCから、チップレット/SiPへの移行は既に始まっている。その理由は2つある。

一つは、必要な集積度が最大サイズチップの限界を超え、必要な集積度を達成するには複数チップを組み合わせる必要が出てきたからだ。例えばBroadcomの製品では5nm世代の半導体製造技術を用いた51.2Tb/sのイーサネットスイッチIC「StrataXGS Tomahawk 5」は1チップといわれているが、次世代の102.4Tb/s品では3nm技術を使用した複数チップ構成になるとみられている。

もう一つは経済的理由だ。最近の微細化技術によるウエハーコストや歩留まりの問題で、最大チップサイズのトランジスタ当たりのコストが増加している。AMDはチップを比較的小型で歩留まりを高くした(コストを下げた)チップに分割し、同一パッケージに搭載することでコストを低減できたという。また、機能ブロックごとに最適なプロセスで製造することにより、性能向上とコスト低減を可能とする。IntelのHPC(High Performance Computing)向けGPU「Ponte Vecchio(開発コード名)」は、5つの異なるプロセスで製造した47チップを同一パッケージに搭載したという。

複数チップを同一基板に搭載したMulti-Chip-Module(MCM)は、以前からあった。最近のSiPはMCMの一種だが、パッケージ内でチップ内と同等の高速な多数の信号線でチップ間を接続することでチップ分割の損失を小さくしている。また、SoCのIPブロックのように標準的に使用できる機能ブロックを最適なプロセスでチップにした、いわゆるチップレットを使用することで設計を容易にし、工数を減らせることに特徴がある(優秀なチップレットはビジネスになるだろう)。

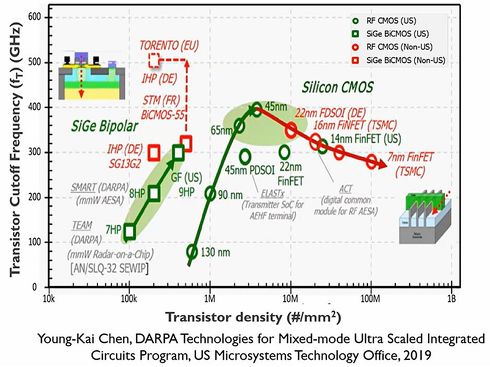

SiP技術は、それに接続されるであろう光インターコネクトに影響があると考えている。図3は米DARPA(国防高等研究計画局)の高速IC開発プログラム「T-MUSIC(Technologies for Mixed-mode Ultra Scaled Integrated Circuits)」で使用された図から必要な部分を取り出した図である。横軸に最大集積度、縦軸にトランジスタの性能指標であるカットオフ周波数(fT)を取り、微細化技術/製造プロセスノードごとにプロットしたものだ。

CMOSでは、微細化により集積度は向上するが、45nmをピークにトランジスタの性能が低下していることが分かる。理由はさておき、このトレードオフは問題である。例えば、イーサネットスイッチICの交換容量は、微細化とその集積度のトレンドに乗って「2年に2倍」のペースで増加しているが、インタフェースのレーン数が同じなので、レーン速度を2倍にしなければならない。このように、集積度と速度向上が要求されるため、インタフェースの速度向上の課題が見える。

しかし、SiPではインタフェースチップレットはロジックと同じプロセスを使用する必要がないため、高速通信に向いたプロセスを利用することができる。このため、高速化が比較的容易になり、光伝送がますます有利になると期待できる。また、インタフェースチップレットの集積度は高くないと予測され、携帯電話の5Gや6G(第5・第6世代移動通信)向けに開発されている高周波IC技術も利用できる。

このチップレット/SiPを効果的に実現するには、チップレットのインタフェースの標準規格が必要である。異なるプロセスだけではなく、異なる設計会社の優れたチップレットを利用することで、経済的にASICが開発できる。Intelが主導したUniversal Chiplet Interface Express(UCIe)は、この標準化を目的に2022年3月に公開された。2023年2月の時点で、100社以上が参加している。

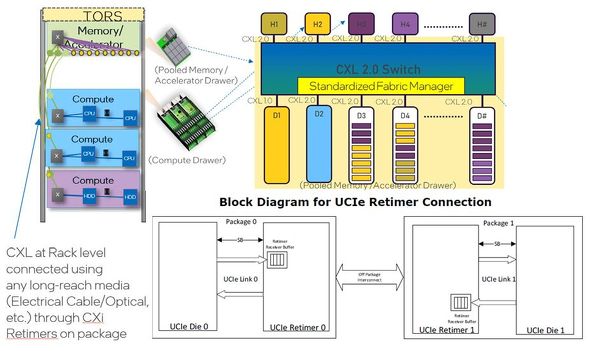

その仕様は公開されている[6]。UCIeは、CXLの実現を意識したものになっており、PCIeベースである。公表当時の標準化の進捗で、PCIe 5.0とCXL 2.0で記述されている。もちろん、現在はPCIe 6.0とCXL 3.0を想定しなければならない。

[6]“Universal Chiplet Interconnect Express (UCIe) Specification,” Revision 1.0, February 24, 2022

光インターコネクト関連では、特に、UCIeリタイマーに注目する。リタイマーはパッケージ間の通信を可能とするインタフェースで、図4にあるようにボード間あるいはラック内配線も想定されている。CXL/PCIeを想定した、リタイマー固有のプロトコルやレジスタなどが定義されている。そして、リタイマーの出力は電気あるいは光となっており、今後の光インターコネクトへの拡張が期待される。

Copyright © ITmedia, Inc. All Rights Reserved.