NVIDIAのGPU不足は今後も続く ボトルネックはHBMとTSMCの中工程か:湯之上隆のナノフォーカス(72)(1/6 ページ)

NVIDIAのGPUが足りていない。需要そのものが大きいこともあるが、とにかく供給が追い付いていない。本稿では、その要因について詳細を分析する。

AIサーバの出荷台数が思ったほど伸びない?

2022年11月にOpen AIがChatGPTを公開して以降、生成AI(人工知能)が爆発的に世界に普及している。その生成AIは、NVIDIAのGPUなどのAI半導体を搭載したAIサーバ上で動作する。

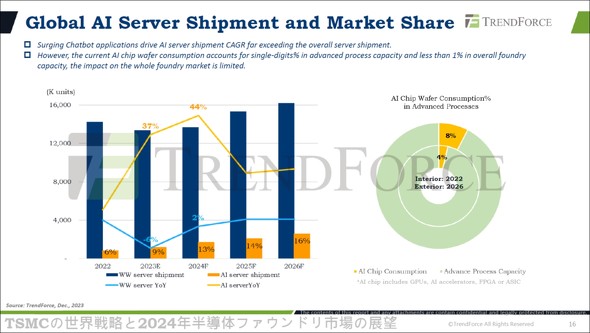

しかし、昨年2023年12月14日に行われた台湾の調査会社TrendForceの予測によれば、AIサーバの出荷台数は思ったほど伸びない。AIサーバが、全てのサーバの出荷台数に占める割合は、2022年に6%、2023年に9%、2024年に13%、2025年に14%、2026年に16%にとどまる予測となっている(図1)。

図1 サーバの出荷台数、AIサーバの割合および、AIチップ用ウエハーの割合[クリックで拡大] 出所:Joanna Chiao(TrendForce)、「TSMCの世界戦略と2024年半導体ファウンドリ市場の展望」(TreendForce産業フォーカス情報、2023年12月14日)のスライド

その理由について、筆者は、拙著記事「半導体の好況は『NVIDIAのGPU祭り』による錯覚? 本格回復は2025年以降か」(2024年3月27日)で、次にように分析した。

この原因はAI半導体の供給律速にあると考えられる。現在、AI半導体の約80%を独占しているNVIDIAのGPUは、TSMCで前工程も後工程も行われている。その後工程では、CoWoSというパッケージングが行われるが、そのCoWoSのキャパシティーがボトルネックになっている。

また、CoWoSにおいては、GPUの周りにDRAMを積層したHBM(High Bandwidth Memory)が複数配置されるが、このHBMもボトルネックの一つになっていると思われる。

では、なぜ、TSMCのCoWoS(Chip on Wafer on Substrate)のキャパシティーが不足する状態が続いているのか。また、DRAMメーカーは、Samsung Electronics、SK hynix、Micron Technologyの3社もあるにもかかわらず、なぜHBMが足りないのだろうか?

本稿では、これらの詳細について論じる。その上で、NVIDIAのGPUなどのAI半導体不足は、今後数年以上続く見通しを述べる。

TSMCが行っている中工程とは

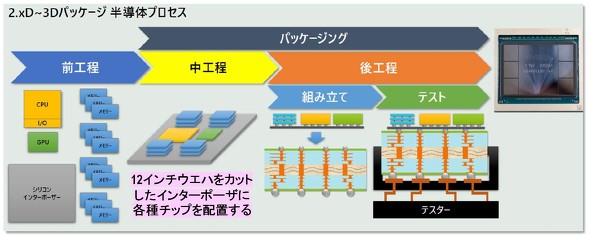

図2は、TSMCにおいて、NVIDIAのGPUがどのように作られているかを示している。まず、前工程で、GPU、CPU、メモリ(DRAM)などが別々に作られる。ここで、TSMCはDRAMを生産していないため、SK hynixなどのDRAMメーカーから、HBMを入手していると思われる。

図2 NVIDIAのGPUなど、2.5D〜3Dで出現する中工程[クリックで拡大] 出所:亀和田忠司、『次世代半導体パッケージング・実装技術動向と市場展望』、サイエンス&テクノロジー主催のセミナー、2024年2月6日のスライド

次に、12インチシリコンウエハーを角型に切断した「シリコンインターポーザー」上に、GPU、CPU、HBMなどを接合する(Chip on Wafer、つまりCoW)。そのシリコンインターポーザーには、チップ間を接続する配線層とシリコン貫通電極(Through Silicon Via、TSV)が事前に形成されている。

そして、これらのプロセスを「中工程」と呼ぶようになっている。その理由を筆者なりに解釈すると、中工程は、分類上は後工程に入るが、シリコンインターポーザー上に形成する配線層などは前工程の製造装置を使って作られている。そのような中間的な意味合いにより、中工程と呼ぶようになったのではないか。

その中工程が完了した後は、インターポーザーを基板に貼り付け(Wafer on Substrate、つまりWoS)、各種テストを行って、CoWoSパッケージが完成する。

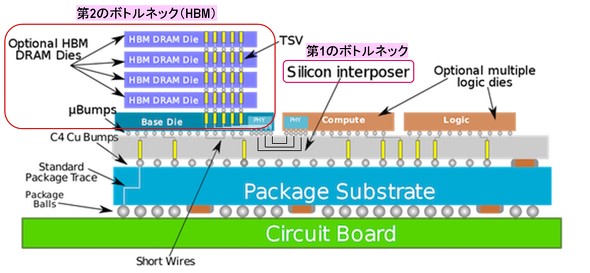

図3は、CoWoSの断面構造を示している。配線層とTSVが形成されているシリコンインターポーザー上に、GPUとCPUなどのLogicチップが2個および、DRAMを積層したHBMが接合されている。そのインターポーザーは、パッケージ基板にC4(Controlled Collapsed Chip Connection)Cuバンプで接続され、その基板はパッケージボールで回路基板に接続されている。

図3 NVIDIAのGPUなどAI半導体のCoWoSの構造と2つのボトルネック[クリックで拡大] 出所:WikiChip、https://en.wikichip.org/wiki/tsmc/cowos

ここで、NVIDIAのGPU不足を引き起こしている原因として、第1のボトルネックが中工程のシリコンインターポーザー、第2のボトルネックがHBMにあると考えている。その根拠を以下で説明する。

Copyright © ITmedia, Inc. All Rights Reserved.