NVIDIAのGPU不足は今後も続く ボトルネックはHBMとTSMCの中工程か:湯之上隆のナノフォーカス(72)(3/6 ページ)

NVIDIAのGPUが足りていない。需要そのものが大きいこともあるが、とにかく供給が追い付いていない。本稿では、その要因について詳細を分析する。

TSMCのCoWoSのキャパシティーが足りない

では、TSMCには、CoWoSの中工程のキャパシティーはどのくらいあるのか。それは十分足りているのだろうか?

2023年11月14日に開催されたDIGITIMESのセミナー”Opportunities and challenges of the global server market in 2024 amid generative AI wave” (Jim Hsiao)では、そのキャパシティーは2023年第2四半期(Q2)に月産13K〜15K枚だったが、2024年Q2に月産30K〜34K枚と倍増し、その結果、NVIDIAのGPUの需給ギャップは解消するとの予測が発表された。

しかし、この見通しは大きく外れた。というのは、2024年の4月時点でも、NVIDIAのGPUは全然足りていないからだ。そして、TrendForceは4月16日のニュースで、TSMCのCoWoSのキャパシティーは2024年末に月産約40K枚となり、さらに2025年末にはこの2倍(月産80K枚?)に拡張することを報じた。やはり、TSMCの中工程のキャパシティーは不足しているのである。

加えてこのTrendForceのニュースには、「H100」の次の世代の「B100」や「B200」がリリースされることが書かれているが、これらのインターポーザーは58mm□よりもっと巨大化するかもしれない。となると、12インチウエハーから取得できる良品インターポーザー数はさらに減るため、TSMCが必死になってCoWoSのキャパシティーを増大させても、需要を満たす数のGPUはできないことになる。

このGPUのCoWoSインターポーザーの巨大化と、TSMCのキャパシティー増大は、どこまで行っても「いたちごっこ」であり、終わることが無い競争(?)と言えるだろう。

この「いたちごっこ」を終わらせる方法として、インターポーザーに、12インチウエハーではなく、515×510mmの角型有機基板を使う案がある。また、米Intelは角型のガラス基板を使うことを提案している。確かに、大型の角型基板を使うことができれば、円形の12インチウエハーより、効率よく多数のインターポーザーを取得できるだろう。

しかし、角型基板上に配線層とTSVを形成するために、それ専用の製造装置や搬送系が必要になる。これらを準備することを考えると、それはそれで時間とおカネがかかり大変である。従って、今のところ、「いたちごっこ」を早期に解決する妙案はないように思う。

今度は、もう一つのボトルネックとなっているHBMの状況について説明したい。

HBMのロードマップとDRAMメーカーの宿命

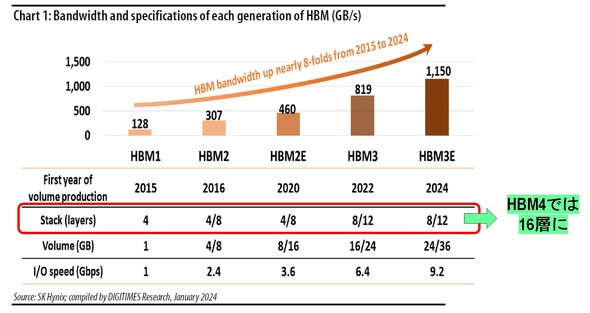

図4や図5で見たように、CoWoSの世代とともにHBM搭載数が増大する。それが、インターポーザーの巨大化にもつながっている。そして、DRAMメーカーは、同じ規格のHBMを作り続ければいいかというと、そうではない。CoWoSの進化とともに、HBMのさまざまな性能を向上させなければならないのである。そのHBMのロードマップを図7に示す。

図7 HBMのロードマップとHBM内に積層されるDRAM数[クリックで拡大] 出所:DIGI TIMES Research, ”HBM Technology and capacity development” (2024年1月)のレポートの図

まず、HBMは、GPUの高性能化に合わせて、1秒間にやりとりするデータの帯域幅(Band width)を向上させていかなければならない。具体的に言うと、2016年のHBM1で128GB/sだった帯域幅は、ことし2024年にリリースされるHBM3Eでは、その約10倍の1150GB/sに拡張される。

次に、HBMのメモリ用容量(GB)を増大させなくてはならない。そのために、HBM内に積層するDRAMチップ数を4枚から12枚へと増やす必要がある。このDRAMの積層数は、次世代のHBM4では、16枚になる見通しである。

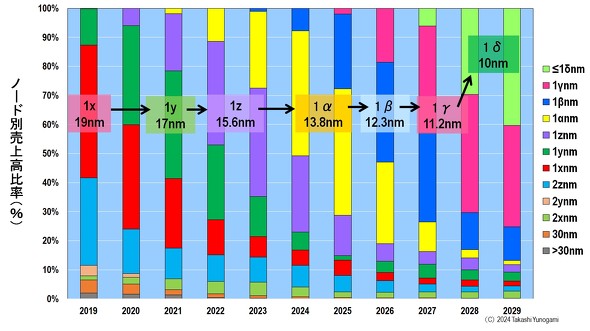

さらに、HBMの動作速度であるI/Oスピード(GB/s)も、向上させていかなければならない。そして、これらを全て同時に実現するためには、何が何でも、DRAMの微細化を進めなければならないのだ。図8は、DRAMのテクノロジーノード別の売上高比率の推移を示す。ことし2024年は、1z(15.6nm)から1α(13.8nm)への切り替えの年である。その後も1β(12.3nm)、1γ(11.2nm)、1δ(10nm)と1nm刻みで微細化を進めることになる。これはDRAMメーカーの宿命かもしれない。

なお、カッコ内の数値は、本当にその世代のDRAMチップの中に存在する最小加工寸法である。最近は素子分離のハーフピッチ(hp)が最も微細なので、その寸法がテクノロジーノードになっている。一方Logicでは、例えばTSMCが3nmを量産していると言っても、その3nmはチップの中のどこを探しても見当たらない。つまり、Logicのテクノロジーノードは、単なる商品名にすぎない。

Copyright © ITmedia, Inc. All Rights Reserved.