チップ部品のリフローはんだ付けにおける「チップ立ち」対策:福田昭のデバイス通信(457) 2022年度版実装技術ロードマップ(81)(1/2 ページ)

今回は、「4.1.3 部品実装・設計時の注意点」の4番目の項目である「4.1.3.4 実装」を取り上げる。実装の不良の要因と対策を説明する。

表面実装のリフローはんだ付けが前提となる不良対策

電子情報技術産業協会(JEITA)が3年ぶりに実装技術ロードマップを更新し、「2022年度版 実装技術ロードマップ」(書籍)を2022年7月に発行した。本コラムではロードマップの策定を担当したJEITA Jisso技術ロードマップ専門委員会の協力を得て、ロードマップの概要を本コラムの第377回からシリーズで紹介している。

第448回からは、第4章「電子部品」の概要説明を始めた。前回は「4.1.3 部品実装・設計時の注意点」の3番目の項目である「4.1.3.3 信頼性」から、「(3)電蝕対策」の概要を述べた。今回は、4番目の項目である「4.1.3.4 実装」の概要をご説明する。

「4.1.3.4 実装」は、「(1)チップ立ち」と「(2)適切なはんだ量の設定」「(3)スルーホールリフロー(THR)対応コンデンサ」の3つの項目で構成される。いずれも表面実装技術の要素技術である「リフローはんだ付け」工程に関連する。以下は順番に各項目の概要を説明していく。

「チップ立ち」不良を発生させる複数の要因

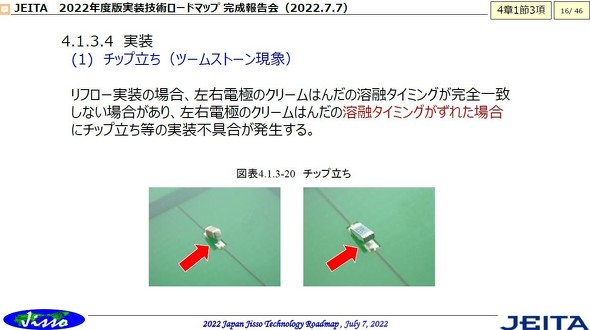

チップ抵抗器やチップ積層セラミックコンデンサ(チップMLCC)などのチップ部品をはんだ付けすると、「チップ立ち」と呼ばれる不良が発生することがある。2つある電極の1つがはんだ付けされず、チップ部品が立ち上がっているように見えることから、「チップ立ち」と呼ばれる。「ツームストーン(Tombstone)現象」(ツームストーンとは墓石のこと)とも呼ばれる。不良モードとしては開放(オープン)状態となる。

チップ部品は平行に並べてレイアウトすることが少なくない。数多く並べたチップ部品の全てあるいは大半がはんだ付け後に立ち上がった不良は「マンハッタン(Manhattan)現象」と呼ばれる。林立したチップ部品が米国ニューヨーク市の高層ビル街区(マンハッタン地区)を連想させることから、名付けられた。

「チップ立ち」不良の基本的な原因は、2つの電極に印刷されたはんだペーストが溶融するタイミングが、電極間でずれたことによる。はんだペーストが早めに溶けて固まった電極側に、チップ部品は引き寄せられ、反対側の電極を上にして立ち上がる。

チップ立ち不良(ツームストーン現象)の発生要因(上)と発生した様子の外観(下)[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

もう少し具体的に述べると「チップ立ち」の原因には、(a)ランドピッチのバランスが悪い、(b)ランド熱容量のアンバランス、(c)リフローはんだ時のはんだ溶融タイミングのばらつき、(d)はんだ量のばらつき、(e)はんだ印刷の位置ずれ、(f)チップ装着の位置ずれ、(g)チップ部品電極のぬれ性の違い、などがある。詳しくはロードマップ本体(書籍)の471ページから473ページを参照されたい。

Copyright © ITmedia, Inc. All Rights Reserved.