連載

チップ部品のリフローはんだ付けにおける「チップ立ち」対策:福田昭のデバイス通信(457) 2022年度版実装技術ロードマップ(81)(2/2 ページ)

今回は、「4.1.3 部品実装・設計時の注意点」の4番目の項目である「4.1.3.4 実装」を取り上げる。実装の不良の要因と対策を説明する。

電極間のばらつき低減とはんだ印刷の均一化が対策の基本

「チップ立ち」不良の対策には、チップ部品側(部品メーカー側)で実施する対策と、実装側(部品ユーザー側)で実施する対策がある。

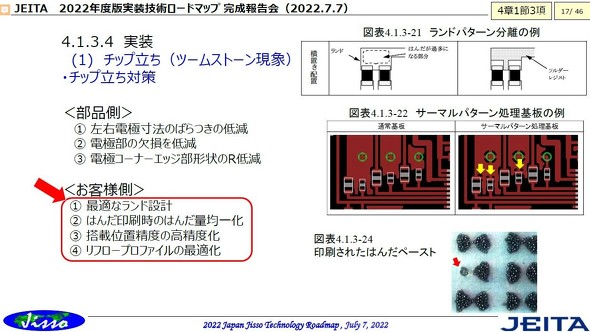

部品メーカー側で実施する対策には、チップ部品の左右電極寸法を均一化する(ばらつきを低減する)、電極部の欠損を低減する、電極コーナーエッジ部の丸みを減らす、などがある。部品ユーザー側(プリント基板の配線パターンとはんだ付け工程)で実施する対策には、最適なランドパターン設計、はんだペースト印刷時のはんだ量均一化、搭載位置精度の向上、リフロープロファイル(温度-時間曲線)の最適化、などがある。

「チップ立ち(ツームストーン)」不良の低減策。左は部品側と部品ユーザー側(はんだ付け側)の対策。右上は広い側のランドにソルダーレジストを被せてランドパターンを電極間で分離し、熱容量を均一化した事例。右中央は電源パターン(通常は配線が太く熱容量が大きい)の電極付近に絶縁部分(「サーマルパターン」と呼ぶ)を作って熱容量を減らした事例。右下ははんだ印刷不良の事例。赤い矢印の部分ではんだペーストが極端に少なくなっている。こうなると「チップ立ち」が起きやすい[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

3端子貫通型フィルタの接続方法と実装レイアウト

3端子貫通型フィルタの接続方法と実装レイアウト

今回は「(2)3端子貫通型フィルタの接続と実装のポイント」の概要を説明する。3端子貫通型フィルタを電源ラインに接続する2つの方法と、それぞれの用途を解説する。 チップ抵抗器の小型化が過度な温度上昇を招く(前編)

チップ抵抗器の小型化が過度な温度上昇を招く(前編)

今回から、第4章第1節第3項「部品実装・設計時の注意点」の概要を説明していく。この項は、「熱設計」「電気性能」などの4つのパートで構成される。 表面実装型電子部品(SMD部品)の開発動向(後編)

表面実装型電子部品(SMD部品)の開発動向(後編)

後編となる今回は、「セラミックコンデンサの高容量化・低ESR化、薄型化」や「チップ抵抗器の高電力化」について解説する。 プロセッサやメモリなどの進化を支えるパッケージ基板

プロセッサやメモリなどの進化を支えるパッケージ基板

今回は第3章第4節第8項(3.4.8)「パッケージ基板」の概要を説明する。パッケージ基板の変遷と、パッケージ基板に対する要求仕様のロードマップを解説する。 表面実装型電子部品(SMD部品)の小型化トレンド

表面実装型電子部品(SMD部品)の小型化トレンド

JEITA「2022年度版 実装技術ロードマップ」を解説するシリーズ。今回から、第4章「電子部品」の概要を説明していく。 プリント基板の「弁当箱」からパッケージとチップまで、電磁シールド技術が進化

プリント基板の「弁当箱」からパッケージとチップまで、電磁シールド技術が進化

JEITA「2022年度版 実装技術ロードマップ」の「パッケージ組立プロセス技術動向」について解説するシリーズ。今回は第3章第4節第6項(3.4.6)「電磁シールド」の概要を説明する。