îΦ™±ëΧ²ΧëOçH£ωÉvÉçÉZÉX²≈êΜëΔ²Ζ²ι¹uÉVÉäÉRÉ™ÉLÉÉÉpÉVÉ^¹v¹Fïü™cèΚ²ΧÉfÉoÉCÉX£ êM¹i460¹j 2022îN™xî≈éάëï΄ZèpÉç¹[ÉhÉ}ÉbÉv¹i84¹j¹i1/2 Éy¹[ÉW¹j

¹u4.2 äνύë†ïîïi¹v²Χ²Λ²Ω¹A¹u4.2.2¹@ÉVÉäÉRÉ™ÉLÉÉÉpÉVÉ^¹v²ΧäT½v²πè–âν²Ζ²ι¹B

äνύë†²Χ½v΄¹²Σ΄≠²Δ觨^^ÉRÉ™ÉfÉ™ÉT

¹@™déqèνïώ΄ZèpéY΄Τ΄Πâο¹iJEITA¹j²Σ3îN²‘²η²…éάëï΄ZèpÉç¹[ÉhÉ}ÉbÉv²πçXêV²Β¹A¹u2022îN™xî≈¹@éάëï΄ZèpÉç¹[ÉhÉ}ÉbÉv¹v¹ièëê–¹j²π2022îN7¨é²…î≠çs²Β²Ϋ¹B•{ÉRÉâÉIJ≈²ΆÉç¹[ÉhÉ}ÉbÉv²Χçτ£η²π£S™•²Β²ΫJEITA Jisso΄ZèpÉç¹[ÉhÉ}ÉbÉvêξ•εàœàθâο²Χ΄Π½Ά²π™Ψ²Ρ¹AÉç¹[ÉhÉ}ÉbÉv²ΧäT½v²π•{ÉRÉâÉIJΧëφ377âώ²©²γÉVÉä¹[ÉY²≈è–âν²Β²Ρ²Δ²ι¹B

¹@ëφ448âώ²©²γ²Ά¹Aëφ4èΆ¹u™déqïîïi¹v²ΧäT½vêύ•Ψ²πén²Ώ²Ϋ¹B²±²ΧèΆ²Ά¹u4.1 SMDïîïi¹v²Τ¹u4.2 äνύë†ïîïi¹v¹u4.3 ÉRÉlÉNÉ^¹v²Χ3²¬²ΧêΏ²≈ç\꧲≥²ξ²ι¹BëOâώ²©²γ¹A¹u4.2 äνύë†ïîïi¹v²ΧäT½v²πè–âν²Β²Ρ²Δ²ι¹Bäνύë†ïîïi²Τ²Ά¹Aäν…™ύë†²Ζ²ι²±²Τ²Σâ¬î\²»ïîïi²πéw²Ζ¹Béσ™°ïîïi²Χ£Ü²≈²ΆÉRÉ™ÉfÉ™ÉT²÷²Χ™ύë†âΜ½v΄¹²Σ΄≠²Δ¹B²±²Χ²Ϋ²Ώ¹u4.2 äνύë†ïîïi¹v²Άäνύ놲Σâ¬î\²»ÉRÉ™ÉfÉ™ÉT¹iÉLÉÉÉpÉVÉ^¹j²≈²†²ι¹A¹u4.2.1¹@î••¨ÉLÉÉÉpÉVÉ^¹v²Τ¹u4.2.2¹@ÉVÉäÉRÉ™ÉLÉÉÉpÉVÉ^¹v²≈ç\꧲≥²ξ²ι¹BëOâώ²Ά¹u4.2.1¹@î••¨ÉLÉÉÉpÉVÉ^¹v²ΧäT½v²π²≤ïώçê²Β²Ϋ¹BçΓâώ²Ά¹u4.2.2¹@ÉVÉäÉRÉ™ÉLÉÉÉpÉVÉ^¹v²ΧäT½v²π²≤êύ•Ψ²Ζ²ι¹B

ëφ4èΆ¹u™déqïîïi¹v²Χéε²»•Ύéü¹mÉNÉäÉbÉN²≈ägëε¹n èoèä¹FJEITA¹@Jisso΄ZèpÉç¹[ÉhÉ}ÉbÉvêξ•εàœàθâο¹i2022îN7¨é7™ζ²…äJçΟ²≥²ξ²Ϋä°ê§ïώçêâο²ΧÉXÉâÉCÉh¹j

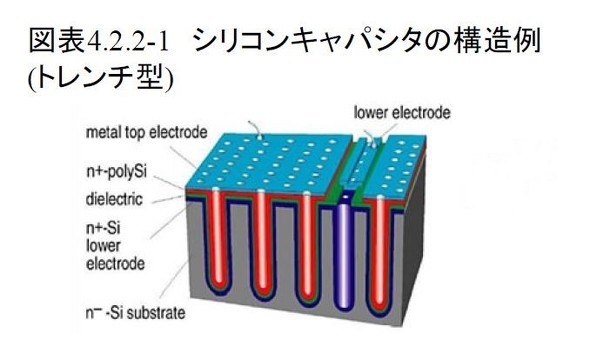

ÉVÉäÉRÉ™²…ê[²Δça²π¨`ê§²Β²Ρ½e½ •ß™x²Χç²²ΔÉRÉ™ÉfÉ™ÉT²πçλ²ι

¹@¹uÉVÉäÉRÉ™ÉLÉÉÉpÉVÉ^¹i¹uÉVÉäÉRÉ™ÉRÉ™ÉfÉ™ÉT¹v²Τ²ύ¨Ρ²‘¹j¹v²Ά¹AÉVÉäÉRÉ™îΦ™±ëΧ²ΧÉEÉGÉn¹[èà½ùçH£ω¹iëOçH£ω¹j²πég²Ν²ΡêΜëΔ²Ζ²ιÉLÉÉÉpÉVÉ^¹iÉRÉ™ÉfÉ™ÉT¹j²≈²†²ι¹BëOçH£ω²≈²Ά¹A¨¥½ù™I²…²Ά2éμ½ό²ΧÉLÉÉÉpÉVÉ^²πçλ²ξ²ι¹B1²¬²ΆÉVÉäÉRÉ™ï\• ²…™±™d•¨²Τêβâ蕨¹A™±™d•¨²Χ3ëwç\ëΔ²π¨`ê§²Ζ²ιêœëw¨^ÉLÉÉÉpÉVÉ^¹iÉXÉ^ÉbÉNÉhÉLÉÉÉpÉVÉ^¹j²≈²†²ι¹Bêœëw¨^ÉLÉÉÉpÉVÉ^²Ά¹ADRAMÉZÉ΄²ΧÉLÉÉÉpÉVÉ^²…çΧ½p²≥²ξ²Ρ²Ϊ²Ϋ¹B

¹@²ύ²Λ1²¬²Ά¹AÉVÉäÉRÉ™²…ê[²Δça¹iÉgɨəÉ`¹j²π¨@²η¹Aça²ΧëΛ• ²Τ£ξ• ²…™±™d•¨²Τêβâ蕨¹A™±™d•¨²Χ3ëwç\ëΔ²πçλ²ηçû²όça¨^ÉLÉÉÉpÉVÉ^¹iÉgɨəÉ`ÉLÉÉÉpÉVÉ^¹j²≈²†²ι¹B¹uÉVÉäÉRÉ™ÉLÉÉÉpÉVÉ^¹v²Ά£ èμ¹AÉgɨəÉ`ÉLÉÉÉpÉVÉ^΄Zèp²≈êΜëΔ²Ζ²ι¹B

¹uÉVÉäÉRÉ™ÉLÉÉÉpÉVÉ^¹iÉVÉäÉRÉ™ÉRÉ™ÉfÉ™ÉT¹j¹v²Χç\ëΔ½α¹BÉVÉäÉRÉ™¹iSi¹jäνiÉVÉäÉRÉ™ÉEÉGÉn¹[¹j²…ça¹iÉgɨəÉ`¹j²π¨@²η¹AÉgɨəÉ`²ΧëΛ• ²Τ£ξ• ²…n+¨^Si•¨²Τé_âΜ•¨¹An+¨^ëΫ¨΄èΜ•¨²Χ3ëwç\ëΔ²π¨`ê§²Β²ΡÉLÉÉÉpÉVÉ^²πçλ²ι¹mÉNÉäÉbÉN²≈ägëε¹n èoèä¹FJEITA¹@Jisso΄ZèpÉç¹[ÉhÉ}ÉbÉvêξ•εàœàθâο¹i2022îN7¨é7™ζ²…äJçΟ²≥²ξ²Ϋä°ê§ïώçêâο²ΧÉXÉâÉCÉh¹j

¹@ÉVÉäÉRÉ™ÉLÉÉÉpÉVÉ^²ΆêœëwÉZÉâÉ~ÉbÉNÉRÉ™ÉfÉ™ÉT¹iMLCC¹j²Τîδ²Ή¹A£Pà • ꜙ•²Ϋ²η²ΧêΟ™d½e½ ¹i½e½ •ß™x¹j²Σç²²Δ¹AâΖ™x²ΣïœâΜ²Β²Ρ²ύêΟ™d½e½ ²Σ²Ό²Τ²ώ²«ïœ²μ²γ²»²Δ¹AàσâΝ™dà≥²ΣïœâΜ²Β²Ρ²ύêΟ™d½e½ ²Σ²Ό²Τ²ώ²«ïœ²μ²γ²»²Δ¹Aç²éϋîgêMçܲ…ëΈ²Ζ²ι™ΝêΪïœâΜ²Σè≠²»²Δ¹A¨oîN½ρâΜ²Σè≠²»²Δ¹A²Τ²Δ²Ν²Ϋ½Dà êΪ²πîθ²Π²ι¹B

Copyright © ITmedia, Inc. All Rights Reserved.