ö╝ō▒æ╠é╠æOŹHÆ÷āvāŹāZāXé┼É╗æóéĘéķüuāVāŖāRāōāLāāāpāVā^üvüFĢ¤ōcÅ║é╠āfāoāCāXÆ╩ÉMüi460üj 2022öNōxö┼Ä└æĢŗZÅpāŹü[āhā}ābāvüi84üjüi2/2 āyü[āWüj

üu4.2 ŖŅö┬ōÓæĀĢöĢiüvé╠éżé┐üAüu4.2.2ü@āVāŖāRāōāLāāāpāVā^üvé╠ŖTŚvéÅąēŅéĘéķüB

āVāŖāRāōŖŅö┬é╔āRāōāfāōāTüAÆ’ŹRüAāCāōā_āNā^éŹņéĶŹ×é▐

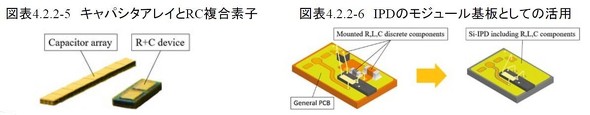

ü@āVāŖāRāōāLāāāpāVā^é═üAé┘é®é╠ľō«ĢöĢiéŹņéĶŹ×é▐é▒éŲé┼ē±śHŖŅö┬éī`ɼé┼é½éķéŲéóéżō┴Æźéö§é”éķüBĢĪÉöé╠āLāāāpāVā^é╔éµéķāAāīāCæfÄqüAāLāāāpāVā^üiāRāōāfāōāTüjéŲÆ’ŹRéłĻæ╠ē╗éĄéĮĢĪŹćæfÄqüAāVāŖāRāōŖŅö┬é╔Æ’ŹRéŲāCāōā_āNā^üAāLāāāpāVā^éÅWÉŽē╗éĄéĮIPDüiIntegrated Passive Deviceüjé╚éŪé╠Ä¢Śßé¬éĀéķüB

āVāŖāRāōāLāāāpāVā^é╠æĮŗ@ö\ē╗Ä¢ŚßüBŹČé═āLāāāpāVā^āAāīāCæfÄqéŲRCĢĪŹćæfÄqüBēEé═Æ’ŹRéŲāCāōā_āNā^üAāLāāāpāVā^éōŗŹ┌éĄéĮIPDüiIntegrated Passive DeviceüjŖŅö┬é╔ē׌péĄé─āvāŖāōāgŖŅö┬é╠ē±śHāéāWāģü[āŗéżī^ē╗éĄéĮŚßümāNāŖābāNé┼ŖgæÕün ÅoÅŖüFJEITAü@JissoŗZÅpāŹü[āhā}ābāvÉĻ¢ÕłŽł§ē’üi2022öN7īÄ7ō·é╔ŖJŹ├é│éĻéĮŖ«É¼Ģ±ŹÉē’é╠āXāēāCāhüj

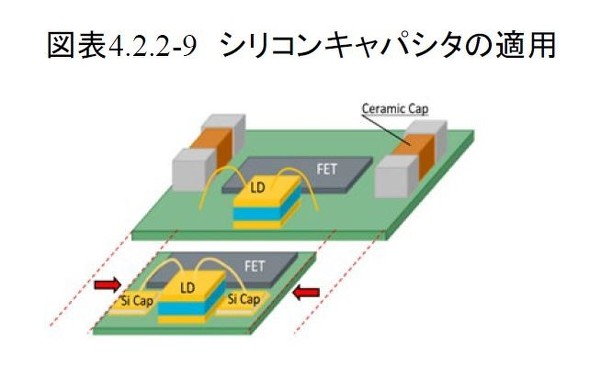

ö╝ō▒æ╠āīü[āUü[é╠āpāŗāXŗņō«ē±śHé╔āVāŖāRāōāLāāāpāVā^éōKŚp

ü@ö╝ō▒æ╠āīü[āUü[üiLDüFLaser Diodeüjé╠āpāŗāXŗņō«ē±śHé╔é═üAÉŽæwāZāēā~ābāNāRāōāfāōāTüiMLCCüjé¬ÄgéĒéĻéķüBāīü[āUü[é╠ÅoŚ═āpāŗāXé═ÅoŚ═ögī`é¬ŗķī`é╔ŗ▀éŁüAÄ×ŖįĢØé¬ÆZéŁüAāsü[āNÅoŚ═鬏ééóé▒éŲ鬢]é▄éĄéóüBéĄé®éĄāRāōāfāōāTéŌözɳé╚éŪé╠Ŗ±ÉČæfÄqé╔éµéĶüAÄ└Ź█é╔é═ÅoŚ═ögī`é═Ŗ█é▌éæčéčüAÄ×ŖįĢØé═ÆĘéŁüAāsü[āNÅoŚ═é¬ÆßéŁé╚é┴é─éĄé▄éżüB

ü@é╗é▒é┼MLCCé╠æŃéĒéĶé╔āVāŖāRāōāLāāāpāVā^éōŗŹ┌éĘéķé▒éŲé┼āpāŗāXŗņō«ē±śHé╠Ģ©ŚØōIé╚ÉĪ¢@éÅké▀üAŖ±ÉČæfÄqéīĖéńéĘüBé▄éĮāpāŗāXŗņō«ē±śHé╠ŖŅö┬é╔āVāŖāRāōé╠IPDāéāWāģü[āŗéō▒ō³éĘéĻé╬üAÅoŚ═ögī`é╠ĢiÄ┐éé│éńé╔Źéé▀éńéĻéķüB

ö╝ō▒æ╠āīü[āUü[üiLDüjé╠āpāŗāXŗņō«ē±śHé╔Ź┌é╣éķāRāōāfāōāTéÉŽæwāZāēā~ābāNāRāōāfāōāTüiMLCCüjüiÅŃÉ}üjé®éńāVāŖāRāōāLāāāpāVā^üiē║É}üjé╔ĢŽŹXéĄéĮŚßüBŗņō«ē±śHæSæ╠éżī^ē╗é┼é½éķümāNāŖābāNé┼ŖgæÕün ÅoÅŖüFJEITAü@JissoŗZÅpāŹü[āhā}ābāvÉĻ¢ÕłŽł§ē’üi2022öN7īÄ7ō·é╔ŖJŹ├é│éĻéĮŖ«É¼Ģ±ŹÉē’é╠āXāēāCāhüj

ü╦üuĢ¤ōcÅ║é╠āfāoāCāXÆ╩ÉMüvśAŹ┌āoābāNāiāōāoü[łĻŚŚ

Copyright © ITmedia, Inc. All Rights Reserved.

ŖųśAŗLÄ¢

üu30öNé╔3000ēŁē~ŗK¢═üvé╠āVāŖāRāōāLāāāpāVā^ü[ÄsÅĻüAīŃöŁāŹü[āĆé¬ī®éóéŠéĘŤŗ@éŲé═

üu30öNé╔3000ēŁē~ŗK¢═üvé╠āVāŖāRāōāLāāāpāVā^ü[ÄsÅĻüAīŃöŁāŹü[āĆé¬ī®éóéŠéĘŤŗ@éŲé═

āŹü[āĆé═2023öN9īÄüAōŲÄ®ŗZÅpéŹ╠ŚpéĄéĮāVāŖāRāōāLāāāpāVā^ü[éöŁĢ\éĄüAō»ÄsÅĻé╔ÄQō³éĄéĮüBīŃöŁéŲéĄé─ÄsÅĻé╔Ʀé▐āŹü[āĆé╔ÉĒŚ¬éĢĘéóéĮüB ōdÄqĢöĢiéŖŅö┬é╔ōÓæĀé│é╣é─Ä└æĢ¢╩ÉŽéīĖéńéĘ

ōdÄqĢöĢiéŖŅö┬é╔ōÓæĀé│é╣é─Ä└æĢ¢╩ÉŽéīĖéńéĘ

ŹĪē±é®éńé═üu4.2 ŖŅö┬ōÓæĀĢöĢiüvé╠ŖTŚvéēÉÓéĘéķüB 3Æ[ÄqŖčÆ╩ī^ātāBāŗā^é╠É┌æ▒Ģ¹¢@éŲÄ└æĢāīāCāAāEāg

3Æ[ÄqŖčÆ╩ī^ātāBāŗā^é╠É┌æ▒Ģ¹¢@éŲÄ└æĢāīāCāAāEāg

ŹĪē±é═üuüi2üj3Æ[ÄqŖčÆ╩ī^ātāBāŗā^é╠É┌æ▒éŲÄ└æĢé╠ā|āCāōāgüvé╠ŖTŚvéÉÓ¢ŠéĘéķüB3Æ[ÄqŖčÆ╩ī^ātāBāŗā^éōdī╣āēāCāōé╔É┌æ▒éĘéķ2é┬é╠Ģ¹¢@éŲüAé╗éĻé╝éĻé╠ŚpōréēÉÓéĘéķüB ā`ābāvÆ’ŹRŖĒé╠żī^ē╗é¬ē▀ōxé╚ēĘōxÅŃÅĖéÅĄéŁüiæOĢęüj

ā`ābāvÆ’ŹRŖĒé╠żī^ē╗é¬ē▀ōxé╚ēĘōxÅŃÅĖéÅĄéŁüiæOĢęüj

ŹĪē±é®éńüAæµ4Å═æµ1É▀æµ3ŹĆüuĢöĢiÄ└æĢüEÉ▌īvÄ×é╠ÆŹłėō_üvé╠ŖTŚvéÉÓ¢ŠéĄé─éóéŁüBé▒é╠ŹĆé═üAüuöMÉ▌īvüvüuōdŗCɽö\üvé╚éŪé╠4é┬é╠āpü[āgé┼Ź\ɼé│éĻéķüB Ģ\¢╩Ä└æĢī^ōdÄqĢöĢiüiSMDĢöĢiüjé╠ŖJöŁō«ī³üiīŃĢęüj

Ģ\¢╩Ä└æĢī^ōdÄqĢöĢiüiSMDĢöĢiüjé╠ŖJöŁō«ī³üiīŃĢęüj

īŃĢęéŲé╚éķŹĪē±é═üAüuāZāēā~ābāNāRāōāfāōāTé╠ŹéŚeŚ╩ē╗üEÆßESRē╗üAö¢ī^ē╗üvéŌüuā`ābāvÆ’ŹRŖĒé╠ŹéōdŚ═ē╗üvé╔é┬éóé─ēÉÓéĘéķüB āvāŹāZābāTéŌāüāéāŖé╚éŪé╠Éiē╗éÄxé”éķāpābāPü[āWŖŅö┬

āvāŹāZābāTéŌāüāéāŖé╚éŪé╠Éiē╗éÄxé”éķāpābāPü[āWŖŅö┬

ŹĪē±é═æµ3Å═æµ4É▀æµ8ŹĆüi3.4.8üjüuāpābāPü[āWŖŅö┬üvé╠ŖTŚvéÉÓ¢ŠéĘéķüBāpābāPü[āWŖŅö┬é╠ĢŽæJéŲüAāpābāPü[āWŖŅö┬é╔æ╬éĘéķŚvŗüÄdŚlé╠āŹü[āhā}ābāvéēÉÓéĘéķüB