AIによる技術革新を加速させるTSMCの最新技術:A16技術やSoW技術の概要を発表(1/2 ページ)

TSMCは横浜で開催した顧客向け技術発表会「TSMC Technology Symposium」に合わせ、テクノロジー専門メディア向けの技術説明会を開催した。説明会では、AIイノベーションを加速させるための半導体製造プロセス「TSMC A16」技術や「TSMC System-on-Wafer(TSMC-SoW)」などについて、その概要を紹介した。

日本での事業規模が拡大、2023年の売上高は41億米ドル超に

TSMCは2024年6月28日、横浜で開催した顧客向け技術発表会「TSMC Technology Symposium」に合わせ、テクノロジー専門メディア向けの技術説明会を開催した。説明会では、AIイノベーションを加速させるための半導体製造プロセス「TSMC A16」技術や「TSMC System-on-Wafer(TSMC-SoW)」などについて、その概要を紹介した。

冒頭、TSMCジャパンの社長を務める小野寺誠氏は、日本市場における事業概要などを紹介した。この中で強調したのは、「AIが第4次産業革命の起爆剤になっている」ということである。日本におけるAI市場は、2023年までに130億米ドル規模へ達するとの予測もある。

小野寺氏は、日本市場におけるTSMCの事業規模について簡単に触れた。1997年に1億5000万米ドルであった売上高は、2010年に6億米ドルとなり、2023年は41億米ドルを超えるなど、順調に推移しているという。また、日本のユーザーに向けたウエハー出荷枚数は2023年に150万枚弱となり、累計では1000万枚(12インチ換算)を超えた。テープアウトの件数も累計で2550件となった。

日本における業績拡大に向けては、サポート体制の強化などに取り組んできた。横浜と大阪にはデザインセンターを、つくばには3DIC R&Dセンターをそれぞれ設け、活動している。さらに、熊本県菊陽町に建設していた「JASM」第1工場も2024年中には量産を始める予定。引き続き、第2工場の建設も進めていくという。

裏面電源供給を採用する「A16」

続いて、TSMCシニアバイスプレジデント兼副共同最高業務執行責任者のKevin Zhang氏が登壇。世界の主要都市で開催してきた「顧客向け技術発表会」において披露された最新のプロセス技術やパッケージ技術などについて、その概要を日本でも説明した。

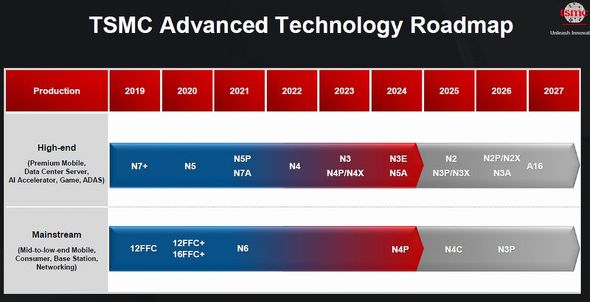

TSMCは既に、3nmファミリーとして「N3E」製品を量産中である。消費電力や性能を向上させた「N3P」技術も提供中で、2024年後半には量産が始まる。これに続くのが2025年後半に生産を始める2nm世代の「N2」技術。

N2の特長は、ナノシートトランジスタに向けた「NanoFlex」が搭載されていることだ。チップ設計者は同一ブロック内で、小さい面積と電力効率が高い「ショートセル」と、性能を最大化する「トールセル」を、組み合わせて集積することができる。この結果、チップ面積と電力効率が同じであれば、速度を15%向上させることができるという。

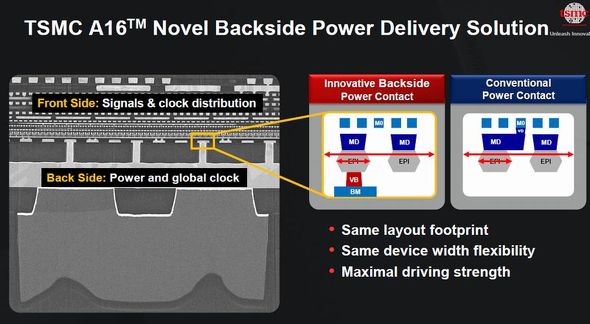

さらに、2026年後半の生産開始を目指す「A16」技術も紹介した。A16は、裏面(バックサイド)から電源を供給する「Super Power Rail(SPR)」アーキテクチャと、ナノシートトランジスタを組み合わせた技術。表面(フロントサイド)の配線リソースを信号専用にすることで、ロジック密度と性能を向上させることが可能となった。

N2Pプロセスに比べると、Vdd(正電源電圧)が同じであれば速度が8〜10%向上し、速度が同じなら消費電力を15〜20%削減できるという。また、データセンター製品では、チップ密度を最大1.10倍向上させることが可能となる。

Copyright © ITmedia, Inc. All Rights Reserved.