AIによる技術革新を加速させるTSMCの最新技術:A16技術やSoW技術の概要を発表(2/2 ページ)

TSMCは横浜で開催した顧客向け技術発表会「TSMC Technology Symposium」に合わせ、テクノロジー専門メディア向けの技術説明会を開催した。説明会では、AIイノベーションを加速させるための半導体製造プロセス「TSMC A16」技術や「TSMC System-on-Wafer(TSMC-SoW)」などについて、その概要を紹介した。

自動車向けプログラムを前倒しして取り組む

「自動車向けプログラム」を前倒しで進めていることも紹介した。日本市場では自動車分野が産業の要となっている。自動車向けの半導体デバイスは、これまで技術が成熟するのを待って用いられてきた。半導体デバイスの信頼性などが重要となるためだ。ただ、高度な自動運転などに対応していくためには、より高性能で高機能な半導体デバイスが不可欠となる。このため、HPCに向けて開発された3〜4nm技術を用いて、自動車向け素子の開発も進めているという。

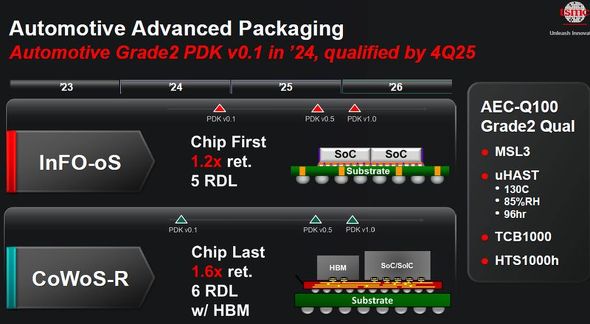

具体的には、2023年にN3AE「Auto Early」プロセスを導入し、先進のプロセス技術とパッケージ技術を統合した製品を提供している。さらに、「InFO-oS(Integrated Fan-Out on Substrate)」や「CoWoS-R(Chip on Wafer on Substrate-RDL Interposer)」といったソリューションを開発中。2025年第4四半期までに「AEC-Q100」グレード2の認定を取得する予定だという。また、車載システム向け半導体デバイスの要件としてZhang氏は、「不良品ゼロに向けて、ロバストな設計基準や効果的なスクリーニングが必要となる」と述べた。

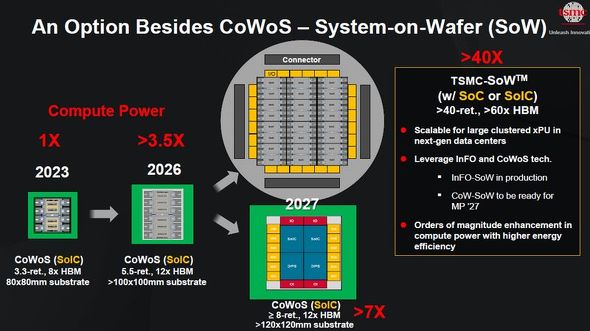

この他、多くのプロセッサコアや広帯域幅メモリ(HBM)スタックを1つのインターポーザ−に並べて実装する「SoW」なども提供。この技術を活用することで、専有面積の削減や演算能力の向上を実現してきた。

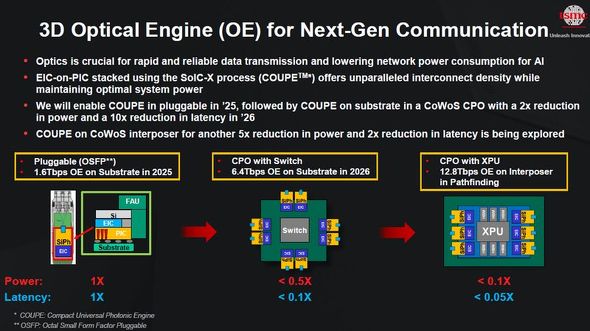

さらに、データ伝送の増加に対応するため、シリコンフォトニクスの統合にも取り組んでいる。開発中のCOUPE(Compact Universal Photonic Engine)技術は、SoIC-Xチップ積層技術を用い、フォトニックダイの上に電気ダイを積層する。TSMCでは、2026年にもCPO(Co Packaged Optics)としてCoWoSパッケージ基板に統合し、光接続機能を取り込む計画である。これにより、消費電力を半分に、レイテンシーを10分の1に削減できる見込みだという。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

TSMCの「A16」は先端プロセス競争を変えるのか

TSMCの「A16」は先端プロセス競争を変えるのか

業界のアナリストたちによれば、TSMCが2024年4月に発表した1.6nm世代の最新プロセス「A16」は、半導体製造プロセスにおける競争を変えるかもしれないという。 SamsungとTSMCの巨額投資、米国サプライチェーンへの影響は

SamsungとTSMCの巨額投資、米国サプライチェーンへの影響は

Samsung Electronics(Samsung)とTSMCは2024年、相次いで米国での半導体製造への巨額投資を発表した。目的としては、現在アジアに偏っている最先端半導体の生産を分散させることや、米国のサプライチェーンにおける半導体の供給源を確保すること、米国の技術的独立を強化することなどが挙げられる。この投資は米国技術に大きな変化をもたらすとみられる。 CHIPS補助金でTSMCがAI半導体製造へ 米国は半導体リーダーに返り咲けるか?

CHIPS補助金でTSMCがAI半導体製造へ 米国は半導体リーダーに返り咲けるか?

TSMCに対する米国の補助金によって、米国は初のAI(人工知能)チップの生産能力を手にし、技術的リーダーシップを確立する強力なチャンスを得るとみられる。ただし、米国の半導体産業の復活のためには労働力不足が依然として大きなマイナス要因だという。米国EE Timesのインタビューでアナリストらが語った。 半導体製造の最先端を独走するTSMCの決算から読み取れること

半導体製造の最先端を独走するTSMCの決算から読み取れること

2024年4月18日、TSMCが2024年第1四半期(1〜3月期)の決算を発表した。ファウンドリー業界で独り勝ち状態のTSMCには、ハイエンドプロセスを中心に需要が集中している。近年の同社決算を振り返り、TSMCの現状や見通しを考えてみる。 TSMCがアリゾナに第3工場を計画、2nm以下を導入し30年までに稼働へ

TSMCがアリゾナに第3工場を計画、2nm以下を導入し30年までに稼働へ

TSMCが、米国アリゾナ州フェニックスに2nm以下のプロセスを導入する第3工場の建設を計画していると発表した。2030年までの稼働開始を目指す。計3工場の建設によって、同州におけるTSMCの設備投資総額は650億米ドル以上となるという。 TSMCが日本に先進パッケージング工場建設か、観測筋は確実視

TSMCが日本に先進パッケージング工場建設か、観測筋は確実視

TSMCが、半導体前工程を担う熊本第一工場に続いて、日本に先進パッケージング工場を建設することを検討していると報じられている。