「UCIe 2.0」の登場で3Dチップレットは加速するか:SiPの試験やデバックも容易に(1/2 ページ)

Universal Chiplet Interconnect Express(UCIe)が、「UCIe 2.0」をリリースした。新たに3Dパッケージングもサポートされる。コンセプト自体は古くから存在するチップレットだが、ここ数年で、標準規格やツールなどが整ってきた。

チップレット技術を規定する標準規格の第2版が登場した。

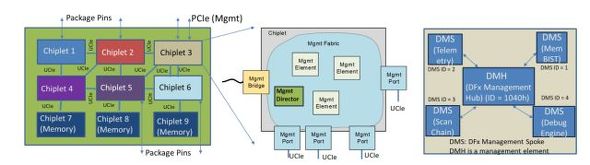

2022年3月に設立されたUniversal Chiplet Interconnect Express(UCIe)コンソーシアムは2024年8月、「UCIe 2.0」仕様をリリースした。今回のアップデートには、複数のチップレットのSiP(System in Package)ライフサイクルにわたるテストのしやすさ、管理のしやすさ、デバッグを考慮した設計(DFx)の課題に向けた対応も含まれる。UCIe 2.0の主な特徴は、チップレットの帯域幅密度と電力効率の劇的な向上を実現する3D(3次元)パッケージングがサポートされたことである。

UCIeコンソーシアムの議長を務めるDebendra Das Sharma氏は米国EE Timesとのブリーフィングで、「UCIe 2.0仕様は完全な後方互換性があり、オプションの管理機能と、ベンダーに依存しないチップレット相互運用性をサポートするUCIe DFxアーキテクチャ(UDA)を導入している」と述べている。

同コンソーシアムは、電気、プロトコル、フォームファクタとコンプライアンス、管理のしやすさとセキュリティ、システムとソフトウェアなど、さまざまな側面に焦点を当てた複数のワーキンググループに仕様に関する作業を分散させている。Das Sharma氏によると、最近結成された自動車ワーキンググループは、自動車分野からの関心を反映して、要件の収集を開始したという。

同氏は、「UCIe 1.0は2Dと2.5Dをサポートするプレーナ型インターコネクト(相互接続)で、これはチップレットが横に並んでいることを意味している。新しい仕様は、必要なコネクティビティ(接続性)に対応することで、チップレットを垂直に積層する3Dスタッキングをサポートしている」と説明している。

Das Sharma氏によると、UCIe 2.0のその他の重要なアップデートは管理のしやすさに関するもので、ダイベースおよびチップレットのパッケージ化した後のデバッグとテストが含まれるという。UCIe 2.0のもう1つの新機能は、相互運用性とコンプライアンステスト向けに最適化されたパッケージデザインである。

UCIe 2.0でサポートされる管理メカニズムには、チップレットとその構成の検出、電力と熱の管理、エラーレポート、チップレットセキュリティのさまざまな側面がある。Das Sharma氏によると、このメカニズムは既存の適用可能な業界規格を活用していて、チップレット上の基本的なプロトコルに依存しないという。また、このメカニズムは、さまざまなベンダーのチップレットで機能し、ベンダー固有の拡張機能をサポートすることも目的としている。

Copyright © ITmedia, Inc. All Rights Reserved.