「UCIe 2.0」の登場で3Dチップレットは加速するか:SiPの試験やデバックも容易に(2/2 ページ)

Universal Chiplet Interconnect Express(UCIe)が、「UCIe 2.0」をリリースした。新たに3Dパッケージングもサポートされる。コンセプト自体は古くから存在するチップレットだが、ここ数年で、標準規格やツールなどが整ってきた。

ハイブリッドボンディングへの移行がトレンドに

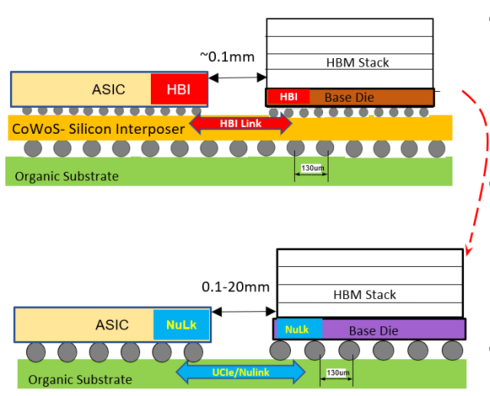

Das Sharma氏は、「チップレットの3Dトレンドの一つはハイブリッドボンディングへの移行で、これはより主流になりつつあり、チップレット間のバンプピッチの積極的な微細化を可能にしている」と付け加えた。3Dインターコネクトではチップレット間の距離がほぼなくなるため、相互運用性は同じバンプピッチに制限する必要がある。

「UCIe-3D」は、10〜25μmから1μm以下のバンプピッチのハイブリッドボンディングに最適化されており、柔軟性と拡張性を提供する。

Das Sharma氏は、「インターコネクトの距離が短いことは電力効率に影響する」と述べる。「チップレット内でも寄生がないため、電力が大幅に低くなる。非常にシンプルな回路だ」(同氏)

Das Sharma氏は、「UCIeは、PCI ExpressやEthernetなど、より成熟したインターコネクトが歩んできた道をたどって、電力効率を最適化しながら2桁の改善を達成することで、帯域幅密度の向上を目指している」と述べる。

「セキュリティ面では、UCIe 2.0は、マネジメントディレクターがRoot of Trust(信頼の根源)として機能する、ハブアンドスポークモデルを採用している。パッケージレベルでセキュリティを強化している」と同氏は付け加えた。

規格やツールがそろい始めたチップレット

チップレット技術は新しいものではないが、ベストプラクティスや標準規格、実装するためのツールの必要性が高まったのはここ数年のことである。2022年後半に、シリコンバレーのスタートアップ企業であるEliyanがステルスモードから脱却し、より効率的なパッケージング手法を提供した。同社の「Bunch of Wires(BoW)」チップレットシステムは、標準的なパッケージングを使用して、高度なパッケージング技術を適用したダイツーダイ実装と同様の帯域幅と電力効率、レイテンシを実現することを目指している。

さらに2024年6月には、同じくチップレット技術を手掛けるスタートアップBaya Systemsがステルスモードから脱却し、チップレット設計の複雑さを解消するための支援を行っている。Baya Systemsのアルゴリズム駆動型システムアーキテクチャプラットフォーム「WeaverPro」は、スケーラブルなIP(Intellectrual Property)およびキャッシュファブリックである「Weave IP」と組み合わせることで、データ駆動型設計と最適化を通じてチップレットアーキテクチャを構築する全てのステップを統合し、チップレットの分析、設計、展開を加速する。

Das Sharma氏は、「UCIe 2.0は、PCIeやNVMeなどのより成熟したインターコネクトプロトコルに倣って、1.0仕様リリースとの下位互換性を目指す」と述べている。

これらの成熟したインターコネクトプロトコルは3年周期で更新されていて、短期間に3つのバージョンが登場したインターコネクト規格「Compute Express Link(CXL)」でさえ、今後は同じパターンをたどる可能性が高い。ただし、「UCIeがどのように落ち着くかは定かではない」とDas Sharma氏は述べている。

「新しいバージョンの多くのワーキンググループには、やるべきことがたくさんある。現時点では、本当にエキサイティングな使用モデルや解決しなければならないことが山ほどある」(同氏)

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「チップレット構想」は破綻してないか? 利点はどこに

「チップレット構想」は破綻してないか? 利点はどこに

昨今、盛り上がっている「チップレット」だが、最近の発表を聞いているとどうにも違和感を覚えてならない。IntelやAMDの製品を取り上げながら、当初提唱されていたチップレットの利点について、もう一度考えてみたい。 ハイブリッドボンディングテストを支援する超音波顕微鏡

ハイブリッドボンディングテストを支援する超音波顕微鏡

ハイブリッドボンディングを高い歩留まりで量産化するには、接合層内部のクラックやボイドなどの欠陥を迅速に特定できる最先端の計測ツールが必要だ。米国の産業用超音波非破壊検査(NDT)システムメーカーであるPVA TePla OKOSは、超音波顕微鏡(SAM)をベースとしたソリューションを手掛けている。 推論性能でNVIDIAに挑む AIチップは「省エネ」が競争の軸に

推論性能でNVIDIAに挑む AIチップは「省エネ」が競争の軸に

推論ベンチマーク「MLPerf」の最新ラウンドのスコアが公開された。その結果からは、AI用プロセッサの新たな競争の軸が、性能そのものよりも「電力効率」に移りつつあることが読み取れる。 600mm角のシリコン基板、三菱マテリアルが開発

600mm角のシリコン基板、三菱マテリアルが開発

三菱マテリアルは、チップレット技術を用いた半導体パッケージに向けた「角型シリコン基板」を開発した。開発した四角形状シリコン基板の外形は「600mm角など世界最大級」(同社)という。 チップレット設計期間をどう短縮するのか 米新興が提案

チップレット設計期間をどう短縮するのか 米新興が提案

チップレットへの注目度が高まるにつれて、チップレット設計における課題も出てきた。米国のスタートアップBaya Systemsは、そうした課題に応えるソリューションを明らかにした。 Intelの先端パッケージング技術「EMIB」を支援するEDAツール

Intelの先端パッケージング技術「EMIB」を支援するEDAツール

Intelのパッケージング技術「Embedded Multi-Die Interconnect Bridge(EMIB)」は、異種統合マルチチップ/マルチチップレットアーキテクチャの複雑化に対処することを目的とした技術だ。EDAツール大手各社が同技術向けのツールを発表している。