特集

3D統合では正確な半導体検査が必須に:歩留まりにも直結(2/3 ページ)

半導体のさらなる高性能化に向けて、3D(3次元)統合/実装が活用されるようになっている。そうした中、重要になっているのが半導体検査だ。半導体検査や計測の精度を上げることは、歩留まりの向上にもつながる。

「ムーアの法則」に連動するインターコネクト密度

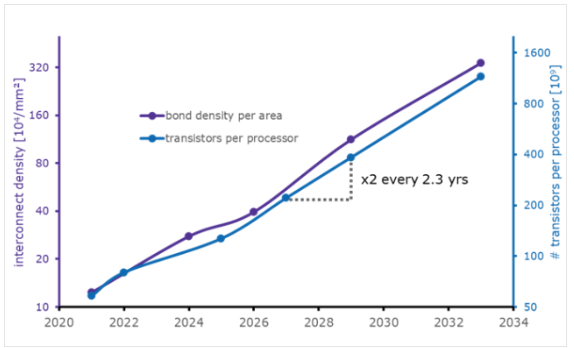

前述のような傾向は、経験的に観測されるだけでなく、図1が示すように定量的にも示されている。

プロセッサ当たりのトランジスタ数は2〜3年ごとに倍増し、古典的なムーアの法則を順守している。興味深いことに、ほぼ同じ割合で増加しているもう1つの指標となっているのが、インターコネクト密度だ。ムーアの法則は1970年代にさかのぼることができるが、インターコネクトは、増加の一途にある半導体チップの帯域幅需要によってもたらされた最近の傾向であり、AIにとって最大の課題の一つになっている。

これらは異なる基準であるにもかかわらず、半導体性能が向上すると、必然的に密接に関連することになる。フロントエンドとバックエンドでは、最先端技術の進展はどちらか一方に依存するためだ。

半導体チップのさまざまな部分を接続するインターコネクト密度が高まることで、複雑性はさらに増す。半導体チップが3Dアーキテクチャへと移行するに伴い、インターコネクトの密度はトランジスタ数と同じくらい重要になっている。インターコネクト密度が高くなれば、AIアクセラレーターやSiP(System-in-Package)ソリューションにとって不可欠なデータ伝送速度も速くなる。だが、エネルギー効率を犠牲にすることなくインターコネクトの数を増加させるには、高性能材料と精度の高い製造技術が必要だ。こうした分野で重要な役割を担うのが計測である。

Copyright © ITmedia, Inc. All Rights Reserved.