L/S 500nm目指す imecが挑む2.5D/3D実装技術:課題は何か(1/2 ページ)

imecは、業界で関心が高まっている2.5D(次元)/3Dインテグレーション技術の研究開発を加速している。EE Times Europeが、imecのシニアフェローに開発の進捗を聞いた。

EE Times Europeは、imecのシニアフェローで3Dプログラムディレクターを務めるEric Beyne氏にインタビューを行い、imecが産業用途向けに準備を進めている新しい2.5D(次元)/3Dインテグレーションのアプローチについて詳細を聞いた。

2.5D/3Dインテグレーションの研究の主要なけん引力となっているのは、メモリユニットとプロセッシングユニットの間のデータ伝送が比較的遅いためにコンピューティング性能が制限される「メモリの壁(Memory Wall)」を乗り越えなければならないというニーズだ。このボトルネックにより、シリコンインターポーザー上での異なるダイとメモリユニットのヘテロジニアスインテグレーションを必然的に必要とするさまざまなアプローチを採用して、チップのすぐ近くにメモリスタックを配置するという取り組みが推進されている。

Beyne氏は、「われわれに必要なのは、チップ間の横方向のインターコネクト技術だ。これは、『2.5D』と呼ぶ場合もある。また、ダイの全面を使用して垂直インターコネクトを作成する3Dインテグレーションも必要である。これは、チップ間の大容量、高速I/Oを主要目的とする場合に効果的だ」と述べている。

2.5Dの研究開発 500nmのL/S実現へ

2.5D技術は、チップレットへと向かう傾向によってもけん引されている。チップレットは、HBM(広帯域幅メモリ)やUniversal Chiplet Interconnect Express(UCIe)などを介して通信する。2つ以上のチップ(またはチップレット)を接続する場合、基板上にブロックを追加する必要がある。そのブロックは、使われる標準規格によって、ブロックとのやりとりをサポートするウルトラファインピッチRDL(再配線層)インターコネクトやシリコンインターポーザインターコネクトを用いた、HBMやUCIeインタフェースブロックになる可能性がある。

Beyne氏は、「われわれは歴史的に、シリコンインターポーザーを使用していた。しかし10年ほど前から、シリコンブリッジに焦点を当てるようになった。そして現在は、ファインピッチのRDLファーストの技術を適用している」と述べる。

Beyne氏によると、2.5D実装技術の研究は2つの分野をカバーしているという。1つはウルトラファインピッチRDLで、imecは現在、500nmのL/S(ライン/スペース)を実現するダマシンRDL技術の方向に進んでいる。これは、業界で現在使われている最小2ミクロンのL/Sよりもはるかに小さい。この500nm L/Sコネクティビティは、有機基板技術を適用することで、一部のシリコンインターポーザーを置き換える可能性がある。

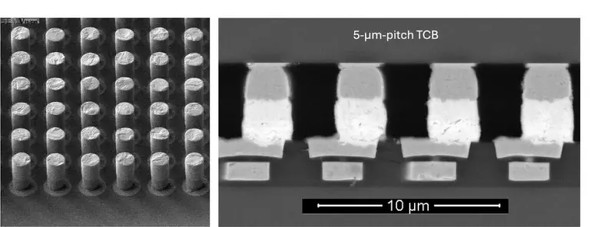

Beyne氏は、「バンプアレイはチップ間のインターコネクトピッチに関連しているため、このようなウルトラファインピッチ接続でのチップの組み立ては、スケーリング則に従うはずだ。われわれは主に、『組み込みマイクロバンプ』と呼ぶ、高さがわずか数ミクロンのマイクロバンプ技術に注力している。5ミクロンピッチまでのスケールダウンが可能だ」と述べる。

「(3Dとは対照的に)2.5Dには、使用するにあたり大きなデメリットが2つある。それは、遅延が長くなることと、より多くの電力が必要になることだ。異なるチップ(チップレット)間の通信に必要なインタフェースブロックによって遅延が生じ、長いラインを超えるために高い電圧が必要になる」(Beyne氏)

Copyright © ITmedia, Inc. All Rights Reserved.