L/S 500nm目指す imecが挑む2.5D/3D実装技術:課題は何か(2/2 ページ)

imecは、業界で関心が高まっている2.5D(次元)/3Dインテグレーション技術の研究開発を加速している。EE Times Europeが、imecのシニアフェローに開発の進捗を聞いた。

3D実装、課題は電力供給

3Dインテグレーションは、インタフェースを追加する必要がない。異なるユニットが、1つのワイヤで接続されているかのように通信するからだ。電圧の変更も必要ない。Beyne氏は、「3Dスタッキングはより高い性能を実現するが、設計プロセスを変える必要があるなどのデメリットもある」と述べる。

「真の垂直統合を実現するには、3Dスタックを協調設計する。システムを3次元に分割し、1つのEDAオペレーションで、全てのユニットの配置配線(place-and-route)と最適化をインタフェースのオーバーヘッドなしで実行するのだ」(Beyne氏)

3Dインテグレーションを採用する場合に生じる懸念は、設計プロセスの再検討だけではない。もう1つ、“パワーウォール”の問題がある。より多くのデバイスを積み重ねると、ユニット当たりの電力密度が高くなり、システムの熱を除去することが難しくなるのだ。

Beyne氏は、「電力密度の高いより大型のシステムから熱を除去するサブシステムが必要だが、同時に、基板からパッケージ、デバイスまでの小さいエリアを介して、3Dスタックのデバイスにより多くの電力(電流の意)を供給する必要がある。1つのソリューションとしては、より高い電圧をパッケージに供給し、その高電圧を、パッケージ内部で、またはチップ/インターポーザーそのものが統合型の電流電圧レギュレーター回路を使用して、低電圧に変換するという方法がある」と述べる。

同氏は、「設計の観点から見ると、チップはさまざまなIP(Intellectual Property)ブロックで構成されている。これらのIPブロック内で、サブセルレベルや標準セルレベル、トランジスタレベルに至るまで、さまざまなレベルで相互接続を作成することができる」と説明する。

「ボンドパスや、外部I/O接続から、グローバルインターコネクトレベル、中間インターコネクトレベル、そして最終的にはローカルインターコネクトへと進んで行く。このため、インターコネクト階層のさまざまなレベルでシステムを分化すると、3次元のインターコネクト密度がますます高くなる」(Beyne氏)

スタックされたコンポーネントは、アプリケーションに応じてレベル1/2/3キャッシュで分割できる。いずれの場合も、相互接続の密度を指数関数的に拡大するには、より小さな相互接続のピッチが必要になる。

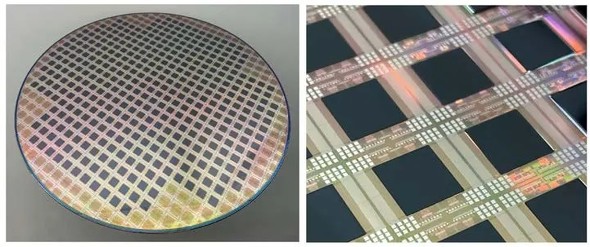

スケールが桁違いであるため、単一の技術でこれらのさまざまな可能性を全てカバーすることはできない。「imecの3Dプログラムでは、これらの分野の多くに積極的に取り組んでおり、主にダイツーウエハー(Die to Wafer)ハイブリッドボンディング、スタッキングおよびマイクロバンプスタッキング、ウエハーツーウエハー(Wafer to Wafer)ハイブリッドボンディングおよびナノTSV(シリコン貫通ビア)集積化に重点を置いている」とBeyne氏は述べている。

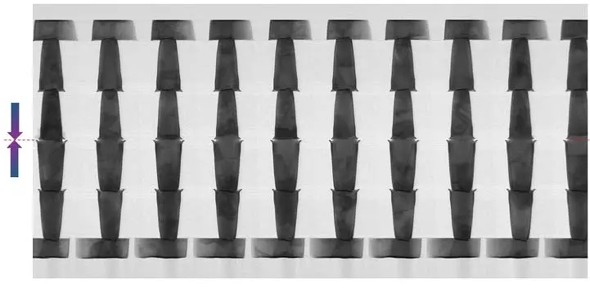

imecは2023年12月に開催された国際学会IEDMで、300mmウエハーのハイブリッドボンディングに成功し、400nmの相互接続ピッチを実現したことを報告した。これには、ウエハー全体でのオーバーレイ制御を100nm未満にする必要があるという。

Beyne氏によると、imecは業界のテクノロジー採用の一歩先を行こうとしている。「われわれはこれをウェハーツーウェハーやダイツーウェハーのボンディングの分野で行ってきたが、裏面ナノTSVボンディングやマイクロバンプアセンブリの分野でも続けている。これら全ての異なるテクノロジーを組み合わせることで、われわれは複雑な3D統合システムという壮大なビジョンに取り組むことができる」

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「UCIe 2.0」の登場で3Dチップレットは加速するか

「UCIe 2.0」の登場で3Dチップレットは加速するか

Universal Chiplet Interconnect Express(UCIe)が、「UCIe 2.0」をリリースした。新たに3Dパッケージングもサポートされる。コンセプト自体は古くから存在するチップレットだが、ここ数年で、標準規格やツールなどが整ってきた。 アナログICを薄膜化して3次元積層、レガシープロセスで

アナログICを薄膜化して3次元積層、レガシープロセスで

日清紡マイクロデバイスと沖電気工業(OKI)が、アナログICをわずか数ミクロンに薄膜化し、それを3次元積層することに成功した。2026年の量産化を目指す。 L/S 1μmを実現するマスクレス露光装置 ニコンが開発へ

L/S 1μmを実現するマスクレス露光装置 ニコンが開発へ

ニコンが、アドバンストパッケージ向けに、1μm(L/S)の高解像度を実現するマスクレス露光装置の開発を進めている。2026年度中の発売を予定しているという。 RapidusとIBM、2nm世代半導体のチップレットパッケージ技術で協業へ

RapidusとIBM、2nm世代半導体のチップレットパッケージ技術で協業へ

RapidusとIBMは2024年6月4日、2nm世代半導体のチップレットパッケージ量産技術確立に向けたパートナーシップを締結したことを発表した。RapidusはIBMから高性能半導体向けのパッケージ技術の提供を受け、技術確立の協業を進める。 開口数0.75の「Hyper-NA」EUV装置 2030年に登場か

開口数0.75の「Hyper-NA」EUV装置 2030年に登場か

ASMLはimecの年次イベントで、次世代のEUV(極端紫外線)リソグラフィ装置のロードマップについて言及した。開口数(NA)が0.75の「Hyper-NA」リソグラフィ装置を開発中だという。