「半導体設計のサイロ化」どう解消? Siemens CEOに聞く:CES 2025(1/2 ページ)

Siemensは「CES 2025」で、デジタルツインソリューション「PAVE360」の最新世代を披露した。サイロ化されがちな設計作業の間の障壁を下げるという。Siemens EDAのCEOを務めるMike Ellow氏に話を聞いた。

Siemensは、米国ネバダ州ラスベガスで2025年1月8〜11日に開催された「CES 2025」において、デジタルツインソリューション「PAVE360」の最新世代を披露した。通常はサイロ化されがちな設計作業の間の障壁を下げるという。米国EE Timesは、Siemens EDAのCEOを務めるMike Ellow氏にインタビューを行い、特に、最近では設計調整のトリクルアップ/ダウン効果をダイナミックに評価する上で、あらゆるシステムレベルでのAIツールの活用が増加しているという点を踏まえ、この設計アプローチが半導体業界にどのように関連するのかという点について話を聞いた。

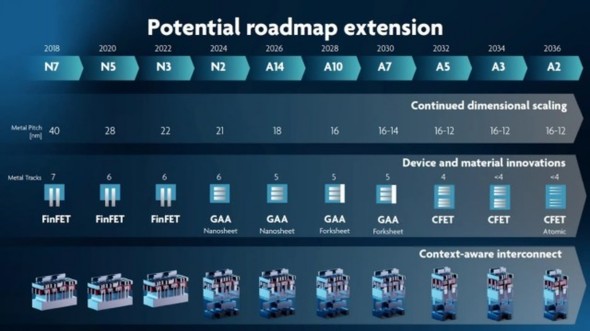

Ellow氏は、IMECのロードマップ(図1)を参照しながら、「半導体業界は、トランジスタサイズに関してある程度の限界に直面しているかもしれないが、微細化はまだ明らかに進んでいる。私は、ムーアの法則が終えんしたと言うつもりはない。なぜならまだ終わっていないからだ。しかし興味深いのは、われわれがこのような大規模なモノリシックSoC(System on Chip)やその製造可能性から、特殊な機能を備えたよりディスクリートなシリコンへと移行していくという点だ」と述べる。

顧客企業はこのようなパラダイムシフトの中で、最大の利益を得るにはプロセス上の機能をどのように最適化すればよいかを決定できる。

同氏は、「電力性能が、面積方程式なのか、コスト方程式、あるいは歩留まり方程式のどれに関するものなのかに関係なく、シリコンパーティショニングをどこに決定するか、またはあるノードで何を行い、別のノードでは何を行うのかを決定するという点で、どのメトリクスをどのように評価したいのかが重要だ」と付け加えた。

Ellow氏は一例としてアナログ/RF回路を取り上げ、「これらは通常、より古い大規模なプロセスノードが適用される一方で、下位の技術ノードでスケールダウンされることはなく、またデジタル回路が他の場所に分離されている」と強調した。

「興味深いのは、3D ICが潤沢な資金を持つ大企業だけのものとされる初期段階(3D ICは非常に高価で難しい)を越えさえすれば、利用可能なシリコンの民主化へと移行できるという点だ」(Ellow氏)

Ellow氏は、「チップレットインターコネクト向けのデータインタフェース規格が策定されれば、チップレットベースの市場は今後5〜7年で大きく進展していくだろう」と予測する。

Copyright © ITmedia, Inc. All Rights Reserved.