キオクシアのNAND戦略 「BiCS FLASH」はどう進化するのか:HCF技術にも言及(1/3 ページ)

キオクシアホールディングスの副社長執行役員である太田裕雄氏が、同社の主力製品である「BiCS FLASH」のロードマップやキーテクノロジー、開発中の新メモリソリューションなどについて語った。

キオクシアホールディングス(以下、キオクシアHD)は2025年6月5日、経営方針説明会を開催。同社の副社長執行役員である太田裕雄氏は、主力製品である「BiCS FLASH」のロードマップやキーテクノロジー、開発中の新メモリソリューションなどについて語った。

「新メモリ技術の多くはキオクシアが生み出した」

太田氏は冒頭、メモリ技術の進化について触れた。AIの普及が顕在化してきた現在、ビット密度向上や信頼性に加え、性能/電力効率など幅広いニーズに応えることで、フラッシュメモリはAIの普及を支えていると説明。またその記憶容量は1991年の4Mビットから、現在量産している第8世代BiCS FLASHでは2Tビットと、50万倍になっているとも述べ、「この過程でSLC、MLC、TLC、そしてQLC(Quad Level Cell)と新しいメモリ技術が生まれたが、この多くはキオクシアが生み出した技術だ。当社は今後も技術革新において業界をリードしていけると考えている」と強調していた。

「最高のビット密度」を実現するキオクシアの技術力

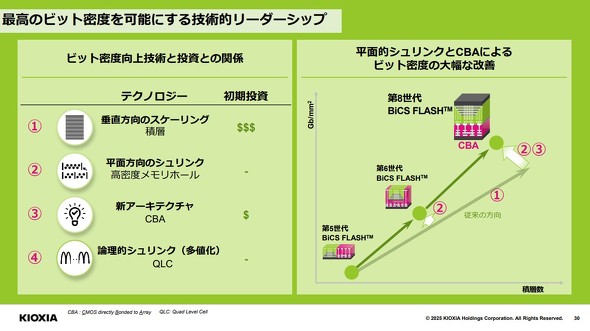

太田氏は「NAND型フラッシュメモリのコスト競争力の源泉は、いかに多くのビットをチップに搭載できるかにかかっている」と強調。一般的にビット密度を高める方法は、積層数を増加させる方法、平面的にチップ面積を縮小させる方法、新規アークテクチャを導入する方法、QLCのように論理的にビット密度を上げる方法の4通りがあるが、「方法によって投資額の大小が変わるので、いかに投資を抑えビット密度を向上させるかが技術開発戦略上、非常に重要だ」と述べた。

キオクシアHDは積層数の増加に加え、平面的に縮小させる方法などを組み合わせることでビット密度の最大化を図っている。太田氏は「一般的に他社は、積層数増によってビット密度を増加させることに注目していると分析しているが、当社はそれに加え、平面方向でのチップ面積の縮小を強みとしている」と説明。さらにCBA(CMOS directly Bonded to Array)などの新規アーキテクチャ導入やQLCの先行導入など、さまざま開発要素によってビット密度の最大化を追求しているとした。

OPSやCBAそして論理的シュリンク

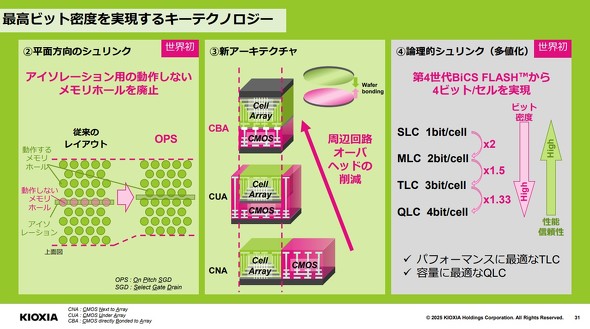

平面方向の縮小技術では、同社がパートナーと共同開発した新技術であるOPS(On Pitch SGD)によって、ワードライン層の面積オーバーヘッド削減を実現している。第6世代BiCS FLASHまでの既存レイアウトでは、物理ページを個別に選択可能にするため、ワードライン層に動作しないメモリホールを作り、物理的なアイソレーションを設けていた。第8世代ではOPS技術を用いることで、このアイソレーションをメモリホールの間に作り、面積的なオーバーヘッドを削減した。

新規アーキテクチャとしてはCBA技術を紹介した。CNA(CMOS Next to Array)からCUAへの移行でCMOSの面積オーバーヘッドは縮小したが、「まだCMOSとメモリセルを接続するための配線オーバーヘッドがあった」と説明。第8世代で導入したCBA技術では、CMOSとセルアレイを個別に加工し貼り合わせることで、このオーバーヘッドをさらに大きく縮小した。太田氏は「この技術についても、キオクシアは業界のトップランナーと自負している。このCBA技術はCMOSウエハー、メモリセルウエハーを最適な温度条件で加工可能になるため、それぞれの最大の性能を引き出すことができ、インタフェース性能、セル性能で非常に競争力のある製品を実現可能にする」と強調していた。

最後に挙げたのは、QLCなどに代表される論理的シュリンク(多値化)だ。キオクシアHDは3次元フラッシュメモリでは第4世代BiCS FLASHからQLCを生産しているほか、2007年に2次元の70nm世代でQLC製品を開発するなど、この分野でも先進的な取り組みを進めてきたと強調。そのうえで太田氏は「QLC製品は、TLC製品から性能、信頼性をトレードオフしながらコストを下げる技術のため、各マーケットからの仕様要求を見極めながら展開している」とも付け加えた。

Copyright © ITmedia, Inc. All Rights Reserved.