乽N2乿SRAM偺曕棷傑傝偼90亾埲忋丂媄弍奐敪傕岲挷偺TSMC丗A16乛A14偺奐敪傕恑傓乮2/2 儁乕僕乯

TSMC偼摨幮屭媞岦偗偺媄弍敪昞夛乽TSMC 2025 Japan Technology Symposium乿傪奐嵜丅TSMC 僕儍僷儞 幮挿偺彫栰帥惤巵丄TSMC Senior Vice President 寭 Deputy Co-COO乮暃嫟摨嵟崅嬈柋幏峴愑擟幰乯偺Kevin Zhang巵偑摨幮偺愭抂僾儘僙僗偵娭偡傞庢傝慻傒忬嫷側偳偵偮偄偰岅偭偨丅

2025擭屻敿検嶻偺乽N2乿丄SRAM偺曕棷傑傝偼90亾埲忋

丂Zhang巵偼乽敿摫懱儅乕働僢僩偺僶僘儚乕僪偑亀AI亁偱偁傞偙偲偼娫堘偄側偄丅AI偑敿摫懱嬈奅傪敳杮揑偵曄偊偰偒偰偄傞乿偲巜揈偟丄乽巹偼栺30擭偙偺嬈奅偵偄傞偑丄偙傫側偵嫽暠偡傞帪婜偼側偐偭偨乿偲弎傋偨丅

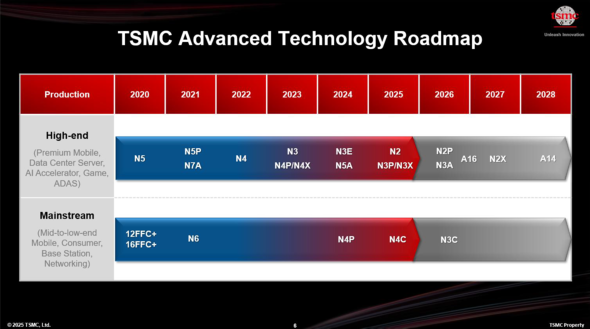

丂TSMC偼2030擭傑偱偵敿摫懱巗応偑1挍暷僪儖偵払偡傞偲梊應偟偰偄傞丅拞偱傕丄崅惈擻僐儞僺儏乕僥傿儞僌乮HPC乯偑巗応慡懱偺45亾丄僗儅乕僩僼僅儞偑摨25亾丄帺摦幵偑摨15亾丄IoT偑摨10亾傪愯傔偰惉挿傪偗傫堷偡傞偲偄偆丅偙偆偟偨廀梫傪庴偗丄TSMC偱偼僄僱儖僊乕岠棪偵桪傟偨墘嶼惈擻偲愙懕惈傪旛偊偨乽N4乿僾儘僙僗丄乽N3乿僾儘僙僗偲乽N6RF乿僾儘僙僗偑寴挷偩丅傑偨丄僨乕僞僙儞僞乕偺媫憹偱5nm偍傛傃3nm愝寁偑恑揥偟丄乽CoWoS乿偍傛傃乽SoIC乿僷僢働乕僕儞僌偵傛傞惈擻岦忋偑壛懍偟偰偄傞偲偄偆丅

丂2nm悽戙偲偟偰偼丄乽N2乿僾儘僙僗偼2025擭屻敿偺検嶻奐巒偵岦偗偰弨旛偑恑傫偱偄傞偲偄偆丅Zhang巵偼乽256M僶僀僩偺SRAM偺暯嬒曕棷傑傝偼90亾埲忋偩乿偲帺怣傪尒偣傞丅乽N2P乿乽N2X乿僾儘僙僗傕弴挷偵奐敪拞偩偲偟偨丅

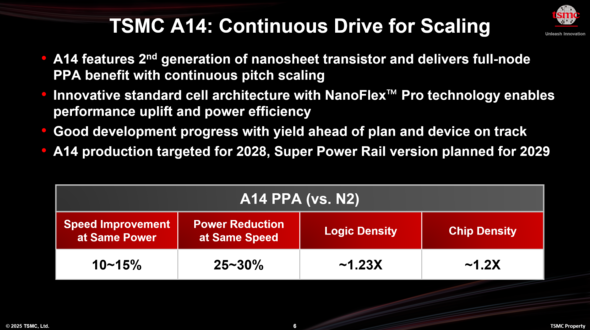

丂2028擭偵検嶻奐巒梊掕偺乽A14乿僾儘僙僗偵偼怴媄弍偱偁傞乽NanoFlex Pro乿傪嵦梡偟丄N2偲斾妑偟偰儘僕僢僋枾搙偑20亾埲忋丄徚旓揹椡摉偨傝偺寁嶼懍搙偑嵟戝15亾岦忋偡傞丅僗儅儂偺AI婡擻傪嫮壔偡傞傕偺偵側傞尒崬傒偩丅

丂2026擭屻敿偵検嶻奐巒傪梊掕偡傞乽A16乿僾儘僙僗偼丄乽嬈奅嵟崅僋儔僗乿乮摨幮乯偺攚柺揹椡嫙媼惈擻偲崅偄儘僕僢僋枾搙偱丄僨乕僞僙儞僞乕岦偗AI乛HPC惢昳偑媮傔傞尩奿側怣崋攝慄偲揹椡嫙媼梫審偵懳墳偡傞丅

丂Zhang巵偼乽AI廀梫偺奼戝偺拞偱嵟傕廳梫側偺偼僄僱儖僊乕岠棪偲墘嶼擻椡偩丅TSMC偼彨棃偺僯乕僘偵崌偭偨宍偱愭抂儘僕僢僋偺奐敪傪恑傔偰偄傞丅TSMC偼儘僕僢僋偩偗偵拲椡偡傞傢偗偱偼側偔丄僾儔僢僩僼僅乕儉僜儕儏乕僔儑儞傪採嫙偟丄屭媞偑枺椡偁傞僨僶僀僗傪嶌傞僒億乕僩傪偟偰偄偔乿偲偟偨丅

Copyright © ITmedia, Inc. All Rights Reserved.

娭楢婰帠

師偼僨乕僞僙儞僞乕丂乽僗儅儂埲奜乿偵傕庤傪峀偘傞Qualcomm

師偼僨乕僞僙儞僞乕丂乽僗儅儂埲奜乿偵傕庤傪峀偘傞Qualcomm

Alphawave Semi傪24壄暷僪儖偱攦廂偡傞偙偲偵崌堄偟偨Qualcomm丅僗儅乕僩僼僅儞偺傾僾儕働乕僔儑儞僾儘僙僢僒偱妋屌偨傞抧埵傪抸偄偰偄傞摨幮偺師偺慱偄偼丄僨乕僞僙儞僞乕偩丅 TSMC偑僪僀僣偵乽墷廈愝寁僙儞僞乕乿怴愝傊丄25擭7乣9寧偵

TSMC偑僪僀僣偵乽墷廈愝寁僙儞僞乕乿怴愝傊丄25擭7乣9寧偵

TSMC偼僆儔儞僟偱奐嵜偟偨僀儀儞僩偵偍偄偰丄僪僀僣丒儈儏儞僿儞偵乽European Design Center乮墷廈愝寁僙儞僞乕乯乿傪愝棫偡傞偲敪昞偟偨丅2025擭戞3巐敿婜乮7乣9寧乯偵奐愝偟丄墷廈偺屭媞婇嬈傪僒億乕僩偟偰偄偔梊掕偩丅 TSMC偼扤偺傕偺丠 暷崙傗AI曃廳偱寽擮偝傟傞乽1杮懌懪朄乿

TSMC偼扤偺傕偺丠 暷崙傗AI曃廳偱寽擮偝傟傞乽1杮懌懪朄乿

TSMC偺2025擭戞1巐敿婜乮1乣3寧婜乯偼岲挷偱丄摨巐敿婜偲偟偰偼夁嫀嵟崅傪峏怴偟偨丅偩偑TSMC偺攧傝忋偘傪暘愅偟偰傒傞偲丄偦偙偵偼柧傜偐側乽堎曄乿偑偁傞偙偲偑暘偐傞丅 僼傽僂儞僪儕乕帠嬈傊偺栰怱擱傗偡Intel丂尞偼乽18A乿

僼傽僂儞僪儕乕帠嬈傊偺栰怱擱傗偡Intel丂尞偼乽18A乿

Intel偺CEO偵Lip-Bu Tan巵偑廇擟偟偰弶傔偰偲側傞巐敿婜寛嶼偑峴傢傟偨丅寛嶼偼摉弶偺梊憐傪忋夞傞寢壥偩偭偨偑丄Intel偑捈柺偡傞怺崗側忬嫷偵曄傢傝偼側偄丅夵慞偺尞偺堦偮偲側傞偺偑僼傽僂儞僪儕乕帠嬈偩丅 TSMC偑1.4nm悽戙僾儘僙僗乽A14乿傪敪昞丄28擭偵検嶻奐巒

TSMC偑1.4nm悽戙僾儘僙僗乽A14乿傪敪昞丄28擭偵検嶻奐巒

TSMC偑丄嵟怴偺1.4nm悽戙偺僾儘僙僗乽A14乿傪敪昞偟偨丅奐敪偼弴挷偵恑傫偱偄偰丄曕棷傑傝岦忋偼乽梊掕傪忋夞傞儁乕僗乿偲愢柧丅2028擭偺検嶻奐巒梊掕偩偲偟偰偄傞丅