講演会場が静まり返った――中国が生み出した衝撃のトランジスタ構造:湯之上隆のナノフォーカス(82)EE Times Japan20周年特別寄稿(6/7 ページ)

EE Times Japan 創刊20周年に合わせて、半導体業界を長年見てきたジャーナリストの皆さまや、EE Times Japanで記事を執筆していただいている方からの特別寄稿を掲載しています。今回は、独自視点での考察が人気のフリージャーナリスト、湯之上隆氏が、2025年の「VLSIシンポジウム」で度肝を抜かれた中国発の論文について解説します。

驚きのFlip FETのプロセス

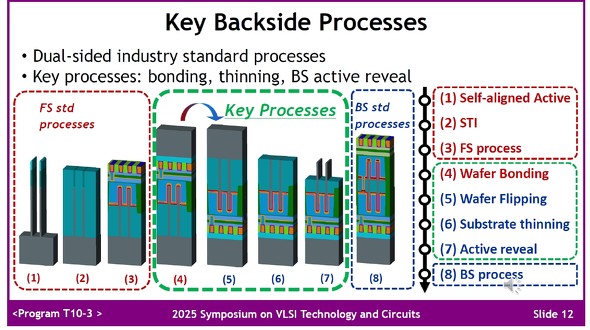

図12を用いて、FrontsideとBacksideに、それぞれ、FETを形成するプロセスについて説明する。

図12 Frontside(FS)とBackside(BS)に別々にFETを形成[クリックで拡大] 出所:VLSIシンポジウム2025、T10-3、Heng Wu(北京大学)、“First Experimental Demonstration of Dual-sided N/P FETs in Flip FET (FFET) on 300 mm Wafers for Stacked Transistor Technology in Sub-1nm Nodes”のスライド

(1)Self-aligned Activeの手法により、FETのチャネル領域を形成する。

(2)素子分離(Shallow Trench Isolation、STI)構造を形成する。

(3)FrontsideにNMOSトランジスタおよびその配線層を形成する。

(4)形成済みのシリコンウエハーに対して、別のウエハーをボンディングする。

(5)ウエハーを上下反転(Flip)させる。これが本プロセスのキーポイントとなる。

(6)反転後、上側になったウエハーを薄化する。

(7)さらにシリコンを除去し、Active層を露出させる。

(8)BacksideにPMOSトランジスタおよびその配線層を形成する。

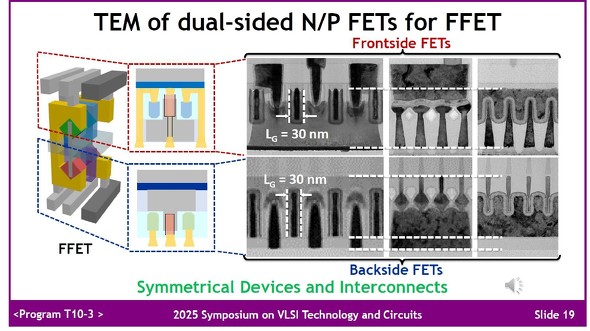

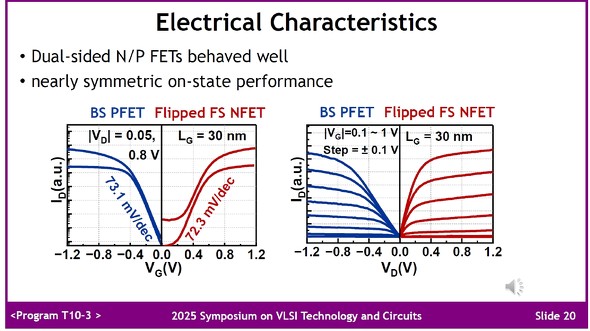

このように、ウエハーを接合した後に反転(Flip)させる工程があることから、本技術はFlip FETと命名された。実際にFlip FETプロセスによって、FrontsideにFinFETのNMOSを、Backsideに同じくFinFETのPMOSを、それぞれ形成した(図13)。そして、NMOSおよびPMOSとも良好な動作が得られた(図14)。

図13 FrontsideにNMOS、BacksideにPMOSを形成[クリックで拡大] 出所:VLSIシンポジウム2025、T10-3、Heng Wu(北京大学)、“First Experimental Demonstration of Dual-sided N/P FETs in Flip FET (FFET) on 300 mm Wafers for Stacked Transistor Technology in Sub-1nm Nodes”のスライド

図14 PMOSとNMOSの動作を確認[クリックで拡大] 出所:VLSIシンポジウム2025、T10-3、Heng Wu(北京大学)、“First Experimental Demonstration of Dual-sided N/P FETs in Flip FET (FFET) on 300 mm Wafers for Stacked Transistor Technology in Sub-1nm Nodes”のスライド

Flip FETの応用編と将来展望

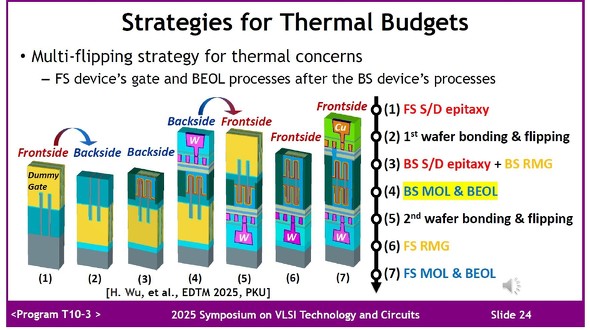

Heng Wu教授は、Flip FETの応用展開として、まずFETのThermal Budgetsの問題に対処するため、BacksideにPMOSおよび配線層を形成した後、FrontsideにNMOSおよび配線層を形成するプロセスを提案した。この手法では、ウエハーの貼り付けと反転(Flip)を2回実行する(図15)。

図15 BSにPMOSをつくってからFSにNMOSをつくるプロセス[クリックで拡大] 出所:VLSIシンポジウム2025、T10-3、Heng Wu(北京大学)、“First Experimental Demonstration of Dual-sided N/P FETs in Flip FET (FFET) on 300 mm Wafers for Stacked Transistor Technology in Sub-1nm Nodes”のスライド

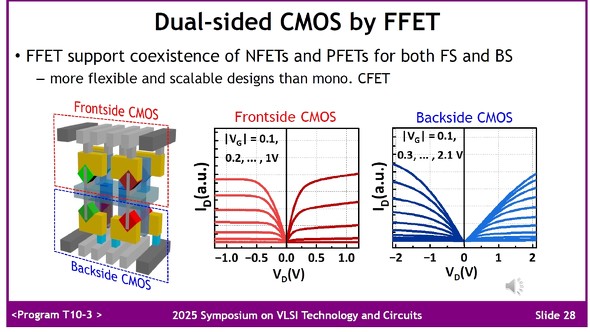

続いて、同じFlip FETプロセスを応用することにより、FrontsideとBacksideのそれぞれにCMOS構造を形成し、その動作特性を評価した(図16)。この内容については、Heng Wu教授の研究グループに所属するYu Liu氏が、TechnologyセッションのT22-4にて発表を行った。

図16 Flip FETにより両面にCMOSが形成できることを実証[クリックで拡大] 出所:VLSIシンポジウム2025、T10-3、Heng Wu(北京大学)、“First Experimental Demonstration of Dual-sided N/P FETs in Flip FET (FFET) on 300 mm Wafers for Stacked Transistor Technology in Sub-1nm Nodes”のスライド

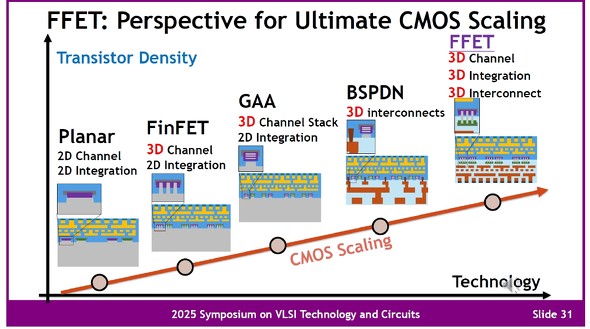

さらにHeng Wu教授は、Flip FET技術をSub-1nmノードへ適用する構想を持っており、そのRoadmapを図17に示している。このRoadmapの詳細は、同研究グループのWanyue Peng氏が、TechnologyセッションT22-3にて発表した。

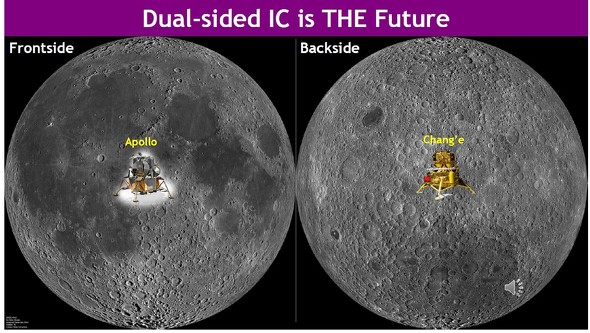

そしてHeng Wu教授は、発表の最後に図18を提示した。月の表側にはアポロ計画によってロケットが着陸したが、将来的には月の裏側への着陸も可能になるかもしれない。それと同様に、半導体技術においても、FrontsideのみならずBacksideにも集積回路(IC)を形成する時代が到来するのではないか──そう結んだ。

図17 CMOSのロードマップにFlip FETを![クリックで拡大] 出所:VLSIシンポジウム2025、T10-3、Heng Wu(北京大学)、“First Experimental Demonstration of Dual-sided N/P FETs in Flip FET (FFET) on 300 mm Wafers for Stacked Transistor Technology in Sub-1nm Nodes”のスライド

Copyright © ITmedia, Inc. All Rights Reserved.