AI/HPCシステムの死命を制する消費電力・放熱設計(前編):福田昭のデバイス通信(511) TSMCが解説する最新のパッケージング技術(8)(1/2 ページ)

「IEDM 2025」におけるTSMCの講演内容を紹介するシリーズ。「(3)Thermal dissipation design(消費電力および放熱の設計)」を前後編に分けて解説する。

消費電力と放熱がシステムの最大性能を制限

2025年12月に開催された国際学会IEDMのショートコース(技術解説)で、シリコンファウンドリー最大手のTSMCが最新のパッケージング技術を説明した。講演のタイトルは「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」、講演者はAdvanced Package Integration Division R&DのディレクターをつとめるJames Chen氏である。大変に参考となる内容だったので、その一部をシリーズでご紹介している。ただし講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演内容を筆者が適宜、補足してある。あらかじめご了承されたい。

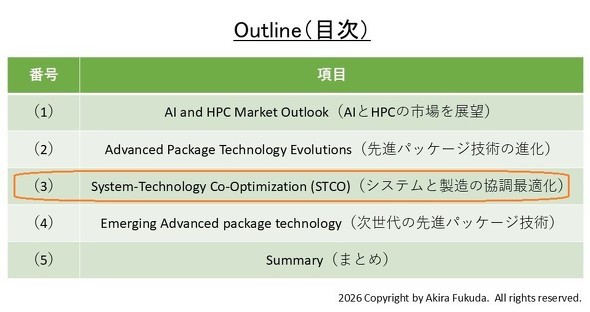

講演「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」のアウトライン[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

タイトルスライドの次に示されたアウトラインは、「AI and HPC Market Outlook(AIとHPCの市場を展望)」「Advanced Package Technology Evolutions(先進パッケージ技術の進化)」「System-Technology Co-Optimization (STCO)(システムと製造の協調最適化)」「Emerging Advanced package technology(次世代の先進パッケージ技術)」「Summary(まとめ)」となっていた。

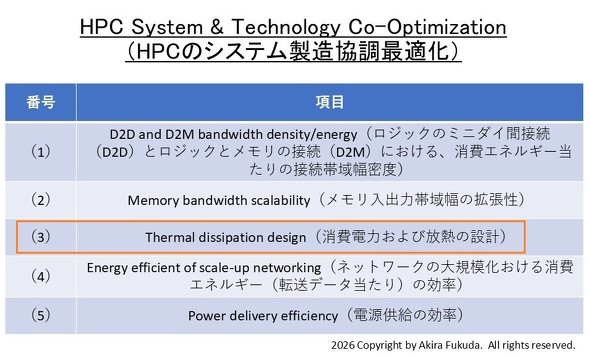

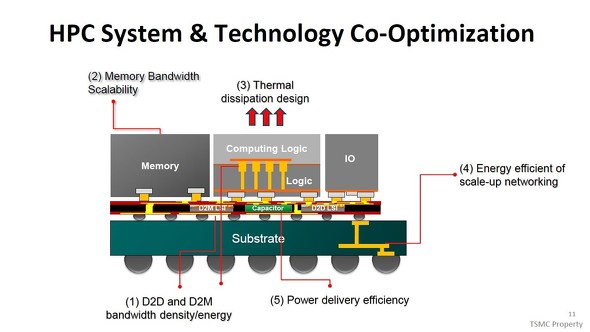

本シリーズの第5回からは、アウトラインの第3項「System-Technology Co-Optimization (STCO)(システム・製造協調最適化)」に相当する部分の説明に入った。先進パッケージ「CoWoS-L(LSI+RDL interposer)」を例に、STCOで考慮すべき5つの項目を順に説明している。

前々回(本シリーズの第6回)では最初の項目「(1)D2D and D2M bandwidth density/energy(ロジックのミニダイ間接続(D2D)とロジックとメモリの接続(D2M)における、消費エネルギー当たりの接続帯域幅密度)」の概要を述べた。前回は、2番目の項目「(2)Memory bandwidth scalability(メモリ入出力帯域幅の拡張性)」をご報告した。今回は3番目の項目「(3)Thermal dissipation design(消費電力および放熱の設計)」を前後編に分けてご説明していく。

STCO(システムと製造の協調最適化)で考慮すべき事柄。先進パッケージ「CoWoS-L(LSI+RDL interposer)」の例[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

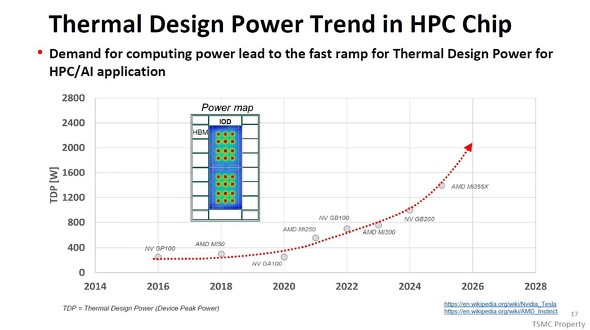

AI/HPCプロセッサの消費電力は過去10年で5倍強に増加

始めはAI/HPCプロセッサの最大消費電力(TDP:Thermal Design Power)がどのように推移してきたかを振り返る。10年前の2016年にはプロセッサ(NVIDIA GP100)のTDPは250W前後だった。それが2018年には300W(AMD MI50)に増える。さらに2021年には560W(AMD MI250)、2023年には700W(AMD MI300)、2024年には1000W(NVIDIA GB200(強制空冷時))、2025年には1400W(AMD MI355X(液体冷却時))と急激に増加している。

なおAMD MI355Xの強制空冷版ともいえるMI350XのTDPは1000Wであり、現行技術による空冷限界が1000W前後にあることが分かる。

Copyright © ITmedia, Inc. All Rights Reserved.