番外編 電源フィルタの設計に悪戦苦闘、雑音を抑えるはずが発振状態に…(後編):Analog ABC(アナログ技術基礎講座)(1/2 ページ)

アンプを設計するとき、まずはアンプの特性をきちんと出さないと話になりません。そこで、電源は理想的だと仮定して、アンプを設計することが多いと思います。アンプの設計が終わって、さて電源フィルタはどうしようかと考え始めると、これが意外と難しいのです。

今回は、前回に引き続き番外編として、アンプの電源フィルタの設計方法を紹介します。

アンプを設計するとき、まずはアンプの特性をきちんと出さないと話になりません。そこで、電源は理想的だと仮定して、アンプを設計することが多いと思います。アンプの設計が終わって、さて電源フィルタはどうしようかと考え始めると、これが意外と難しいのです。「時間切れなので、後は試作したチップを測定しながら調整しよう」というパターンが悪戦苦闘の始まりです。

アナログ回路は、周辺の回路を配慮して設計しないと、性能をうまく発揮しなかったり、動作しなくなったりする…。当たり前のことですが、なかなか実行できないことが多いのではないでしょうか。

電源のわずかな変動が悪影響

前回紹介した通り、電圧源の雑音を除去する電源フィルタは、アンプに不可欠な回路です。電源に重畳したスイッチングレギュレータの雑音などが、アンプの誤動作を引き起こさないようにするために、電源とアンプの間に電源フィルタ挿入します。

前回は、インダクタL1とコンデンサC1、ダンピング抵抗R1で、低域通過フィルタ(LPF:Low Pass Filter)を構成しました。インダクタL1とコンデンサC1だけで、LPFを構成すると、並列共振を起こしてしまい、アンプの電源電圧VCC2が、アンプ自身の電流でゆすられてしまいます。そこで、ダンピング抵抗R1を追加し、並列共振の鋭さ(Q値)を下げる対策を採りました。

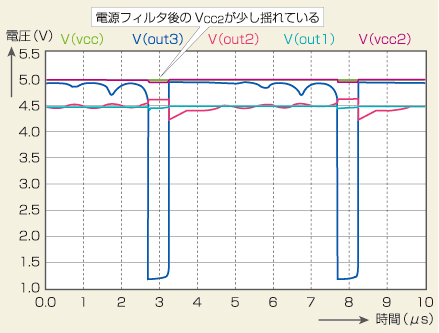

しかし、ダンピング抵抗を入れた後も、電源に雑音が載るたびに、大きなパルスが出力されてしまい、正しく動作しませんでした(図1)。図1を見ると、VCC2のわずかな変動が、出力電圧V(out3)へ大きな変動となって表れてしまっています。電源フィルタを通過した後の電源電圧VCC2がゆれると、どうも具合が悪いようです。なぜでしょうか…。

図1 電源電圧VCC2のわずかなゆらぎが出力へ悪影響を及ぼす 電源フィルタの後の電源電圧VCC2のわずかなゆらぎが、出力電圧V(out3)の大きな変化となって表れています。これを防ぐには、新たな対策を施す必要があります。

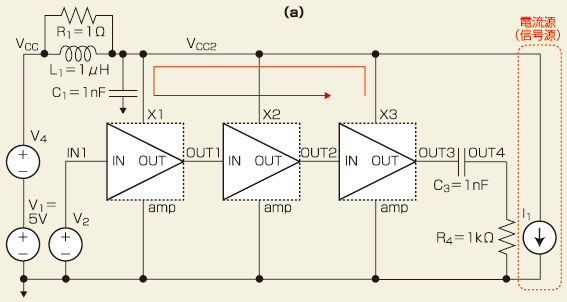

原因を探ってみましょう。図2(a)は、アンプ回路にインダクタL1とコンデンサC1、ダンピング抵抗R1で構成した低域通過フィルタを追加した回路です。電源電圧VCC2がゆれたとき、アンプの各段に何が起こっているのか把握するために、交流(AC)解析を施してみます。

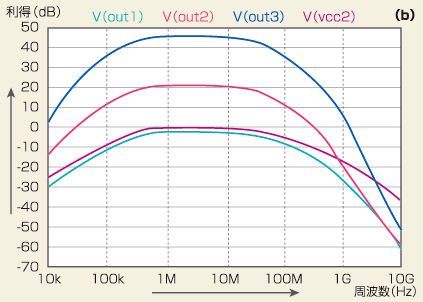

図2 交流(AC)解析で出力電圧の利得を確認 (a)は、アンプ回路に電源フィルタとして、インダクタL1とコンデンサC1、ダンピング抵抗R1で構成した低域通過フィルタを追加した回路です。AC解析を施す際の信号源として、電流源を挿入してあります。次ページの(b)は、AC解析の結果で、各出力電圧と電源電圧VCC2の利得を示しています。電源電圧VCC2のわずかな変動が、V(out3)へ大きな変動となって表れます。

電源電圧VCC2がゆれる原因は、アンプの消費電流が変化することにありますので、AC解析の信号源として、電流源を使います。図2(b)に、AC解析の結果として、各アンプの出力電圧や電源電圧VCC2の周波数特性を示しました。電流源の電流変化に対する、出力電圧や電源電圧VCC2の変化の具合(揺すられ具合)を、利得(dB)として表現しています。利得が高いほど、激しく揺すられていることになります。

例えば、VCC2の利得を見ると、1MHzを切るような低い周波数ではインダクタL1が、10MHzを超えるような高い周波数ではC1が効いて利得が低下しています。ところが、1MHzから10MHzの間では、利得は低下せずに、0dBとなっています。

Copyright © ITmedia, Inc. All Rights Reserved.