第28回 カレントミラーで2つのMOSFETの歩調を合わせる:Analog ABC(アナログ技術基礎講座)(2/2 ページ)

前回紹介した増幅回路は、2つのMOSFETのしきい値(Vth)のわずかなずれが、利得や動作点に大きな影響を与えるという欠点がありました。今回は、欠点をどのように改善するかを紹介しましょう。

ゲート接地で応答速度を向上

能動負荷を使い利得を高めた増幅回路で発生する課題として、応答速度が遅くなることが残っています。この課題への対処方法を紹介しましょう。

応答速度が遅くなるのは、MOSFET(M3)のゲートとドレインの間に寄生する静電容量Cgdが原因です。増幅回路の入力と出力の間にある静電容量なので、ミラー効果によって静電容量が利得倍に増えて、応答速度の低下を引き起こしてしまうのです。

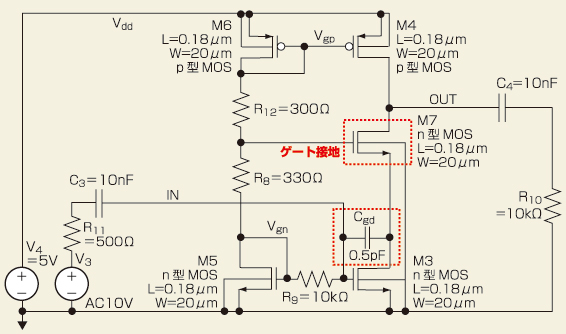

ミラー効果を抑制するために、図1の増幅回路にさらにゲート接地回路を追加しました(図3)。ゲート接地回路は、バイポーラトランジスタのベース接地回路と同じ効果が得られ、応答速度を高められます。(ミラー効果やベース接地回路の動作については、第10回の「エミッタ接地回路のサプリメント 〜 ベース接地回路 〜」を参照して下さい)

図3 ゲート接地回路を追加した増幅回路 応答速度を高めるために、図1にさらにゲート接地回路を追加しました。バイポーラトランジスタのベース接地回路と同様に、ミラー効果を抑制し、増幅回路の応答速度を高める効果が得られます。

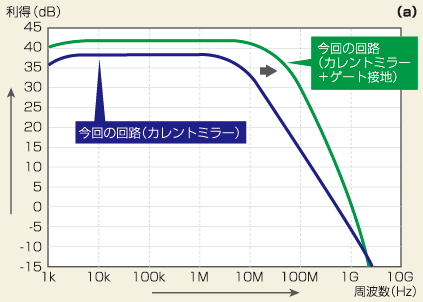

図4(a)に、ゲート接地回路を使ったミラー効果対策を施した増幅回路の交流解析の結果を示しました。ゲート接地回路の効果は一目瞭然で、高域遮断周波数がおよそ10MHzから100MHzに向上しました。

また、高域遮断周波数よりも低い周波数帯域で、利得が2dBほど高くなっていることも分かります。これは、M3とM7がカスケード接続されたことで、より出力インピーダンスが高くなり、理想的な電流源に近づいたためです。

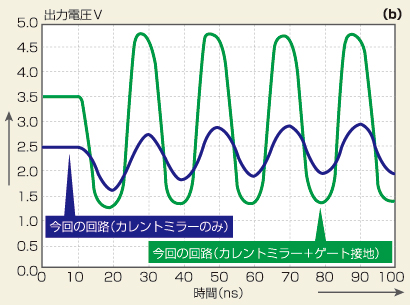

図4 ゲート接地回路を追加した効果 図上の(a)は利得の周波数特性です。ミラー効果を抑えたことで周波数特性が改善し、高域遮断周波数を高めることができました。また、図3のM3とM7がカスケード接続されたことで、利得も向上しています。図下の(b)は過渡解析の結果です。利得向上に伴って、振幅が大きくなったことを確認できました。

図4(b)に過渡解析の結果を示しました。周波数が50MHz、振幅が100mVppの信号を図3の回路に入力したときの出力です。ゲート接地回路を追加した方が、振幅が大きくなっていることを確認できました。

次回は、これまで紹介してきた幾つかの要素回路を組み合わせましょう。バイポーラトラジスタを使って紹介した差動対と、MOSFETの増幅回路を組み合わせた回路を解説する予定です。

Copyright © ITmedia, Inc. All Rights Reserved.