世界人口に相当するトランジスタが45mm角に、Xilinxが最大規模のFPGA出荷:プログラマブルロジック FPGA(2/2 ページ)

単一のパッケージに複数のFPGAチップを納める独自技術を適用することで実現した最大規模品である。ロジック規模はASICゲート換算で2000万〜4000万ゲートに相当し、トランジスタ数は68億個に達する。出荷を開始したのはエンジニアリングサンプル品で、量産品の出荷は2012年第4四半期の予定だ。

ASICプロトタイピングや無線インフラ向けネットワークスイッチを狙う

XilinxがVirtex-7 2000Tでまず狙う用途は、大規模ASIC開発のプロトタイピングやエミュレーションである。ASIC開発時に、ASIC上に構成する回路を検証したり、試作チップの完成を待たずにソフトウェアの開発を進めたりするために、ハードウェアエミュレータとしてFPGAを使う。実際に、「現時点でVirtex-7 2000Tを発注している顧客企業は、ASICプロトタイピング向けだ」(XilinxのDouglass氏)という。ロジック規模が大きいこの品種を使えば、複数のFPGAを組み合わせて構成したエミュレーションボードを用いる場合に比べて、ASICの回路を複数のFPGAに割り付ける複雑な作業が軽減される上に、FPGA間をボード上でつなぐインタフェースの速度によって処理性能が制限されてしまうことが無いというメリットがある。

次にXilinxが視野に入れるのは、ASICそのものの代替だ。同社は前述の通り、ASICゲート換算で2000万〜4000万ゲートの規模のロジックをVirtex-7 2000Tに搭載できるとしており、そうした大規模ASICの置き換えを狙う。「ASICは開発コストが高騰しており、大規模品では5000万米ドルに達する場合もある。一方で、その巨額の投資を回収できる量産規模のASICは減少傾向にあり、そこにFPGAの商機がある」(同氏)。

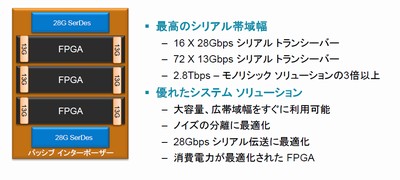

同社は2000万ゲートを超える規模のASICの具体例として、無線通信インフラ向けのネットワークスイッチなどを挙げている。ただしそうしたASICでは、極めて広い帯域幅でデータを入出力することが求められる。そこで同社は、スタックド シリコン インターコネクト技術を適用する品種の拡充を進める考えだ。具体的には、パッケージ内に複数搭載するFPGAダイそれぞれに13Gビット/秒動作の高速シリアルトランシーバ(SerDes)回路を集積する品種群「Virtex-7 XT」や、28Gビット/秒動作の高速シリアルトランシーバ回路を単独のダイとして別に用意し、複数のFPGAダイとともに単一のパッケージに納める品種群「Virtex-7 HT」である(図5)。Virtex-7 HTの最大規模品では、入出力帯域幅は2.8Tビット/秒に達するという。

図5 ヘテロジニアスなマルチチップ構成へ展開 スタックド シリコン インターコネクト適用品の第1弾となるVirtex-7 2000Tは、FPGAダイのみを複数枚まとめた“ホモジニアス”なマルチチップ構成だが、今後XilinxはFPGAダイと別種のダイを組み合わせる“ヘテロジニアス”品も投入する。まずは、28Gビット/秒の高速シリアルトランシーバ回路を個別のダイとして用意し、それを搭載した品種から供給する計画だ。出典:Xilinx

Copyright © ITmedia, Inc. All Rights Reserved.