「20nmプロセスはダブルパターニングがコスト増要因に」、TSMCのCTOが明かす:プロセス技術

TSMCは、20nmプロセスの試験生産を2012年第3四半期から開始する。しかし、同プロセスに採用したダブルパターニングによって、28nmプロセスと比べて製造コストが増える見込みだ。

TSMC(Taiwan Semiconductor Manufacturing Company)は2011年11月28日、横浜市内で記者会見を開き、20nmプロセスをはじめとする製造技術の開発状況を報告した。

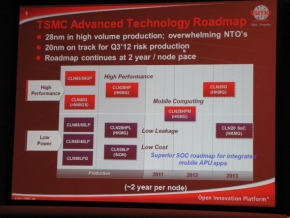

会見に出席した、同社で研究開発担当副社長兼CTO(最高技術責任者)を務めるJack Sun氏は、「20nmプロセスは、2012年第3四半期から、高性能アプリケーション向けの『CLN20G』のリスク生産(試験生産)を始める。一方、より低消費電力が求められるモバイル機器向けの『CLN20 SoC』は、2013年1月にはリスク生産が可能になるだろう。14nmプロセス以降も、2年ごとに1世代進化する製造プロセスのロードマップを維持する方針である」と語った。

左の写真がTSMCのJack Sun氏。右の図は、TSMCのロジックIC向け製造プロセスのロードマップである。赤色が高性能アプリケーション向けのプロセス、青色が低消費電力アプリケーション向けのプロセスとなっている。

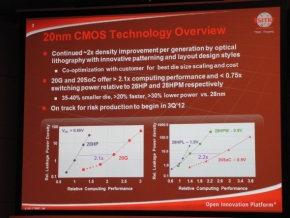

左の写真がTSMCのJack Sun氏。右の図は、TSMCのロジックIC向け製造プロセスのロードマップである。赤色が高性能アプリケーション向けのプロセス、青色が低消費電力アプリケーション向けのプロセスとなっている。今回発表した20nmプロセスは、2011年から量産を始めている28nmプロセスと比較すると、2.1倍以上の処理性能を引き出せるとともに、消費電力も3/4以下に低減できる。露光技術は、ArF(フッ化アルゴン)光源の液浸露光装置によるダブルパターニング(1つの回路パターンを2つの密集度の低いパターンに分割して露光する技術)を用いている。ウェハーの処理速度については、「装置メーカーの仕様では100枚/時以上となっている。リスク生産までにこの処理速度を実現できるようにしたい」(Sun氏)という。また同氏は、20nmプロセスの製造コストについて、「28nmプロセスと比べると、ダブルパターニングの採用がコスト増の要因になっている。今後のプロセス選択は、開発対象のICの要件を考慮した上で最適なダイサイズやコストを実現できるように、当社と顧客が協力して検討しなければならないだろう」とコメントしている。

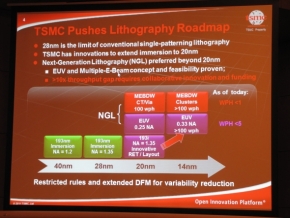

14nmプロセスへの適用に向けて開発が進められているEUV(極端紫外光)とMEBDW(マルチ電子ビーム直描)などの次世代露光技術では、100枚/時以上の処理速度が求められているものの、現時点ではEUVが5枚/時、MEBDWが1枚/時にとどまっていることが明らかになった。この他、3次元トランジスタ構造であるFin-FETを、14nmプロセスから提供する方針も示された。

左図内のグラフは、20nmプロセスと28nmプロセスの性能を比較したもの。右の図は、TSMCが各プロセスで採用している露光技術である。20nmプロセスはタブルパターニングを採用した。EUVやMEBDWといった次世代露光技術は14nmプロセスで利用すべく開発が進んでいる。

左図内のグラフは、20nmプロセスと28nmプロセスの性能を比較したもの。右の図は、TSMCが各プロセスで採用している露光技術である。20nmプロセスはタブルパターニングを採用した。EUVやMEBDWといった次世代露光技術は14nmプロセスで利用すべく開発が進んでいる。また、BSI(裏面照射型)イメージセンサーは、2013年末までに0.9μmプロセスを用いた生産を始められるようにする。同プロセスを用いることで、現在量産中の1.4μm/1.2μmプロセスよりも大幅な微細化が可能になる。

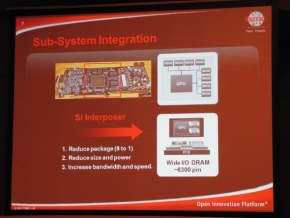

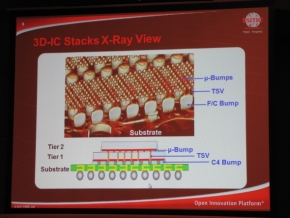

3次元パッケージングについては、シリコンインターポーザで複数のチップ間を接続して1パッケージ化する技術を開発している。2012年には、同種のダイを接続するものの量産を始める。プロセッサとメモリなど異なる種類のダイを接続するものについては、2013年から2014年に量産を始める計画だ。シリコンインターポーザの製造コストは、「現時点でTSMCの想定の2倍となっているため、装置サプライヤなどと協力してコスト低減を進める」(Sun氏)方針だ。

これらの3次元パッケージングに用いるシリコンインターポーザは、配線構造を作り込んでいるだけで、トランジスタなどの素子構造を持たない。一方、トランジスタなどの素子構造を持つダイに貫通シリコンビア(TSV)を設けてダイを積層するタイプの3次元パッケージングの実用化時期は2014年以降になる見込みだ。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

TSMCの14nm世代への移行は遅れる可能性も、「原因は経済的な問題」

TSMCの14nm世代への移行は遅れる可能性も、「原因は経済的な問題」

TSMCの14nmプロセスへの移行が、スケジュール通りにはいかない可能性が出てきた。同社のShang-Yi Chiang氏は、この原因を「技術的な問題というより、経済的な問題である」とし、「リソグラフィ技術の選択について決断を急ぐ必要がある」と語った。 「半導体微細化、技術的には7nmも可能」、TSMCの開発責任者がARMイベントで言及

「半導体微細化、技術的には7nmも可能」、TSMCの開発責任者がARMイベントで言及

半導体製造プロセスの微細化は、3次元構造を利用すれば7nmノードも不可能ではないという。だが、問題は技術ではなくコストにある。- TSMCが電子ビーム・リソグラフィ装置を導入、目標は22nm製造技術の先か