第35回 あの手この手でBand Gap Referenceの電源雑音対策:Analog ABC(アナログ技術基礎講座)(1/2 ページ)

第33回、第34回に分けて、さまざまな電子回路の基準電圧を生み出すBand Gap Reference(BGR)回路を設計してきました。幾つかの残された課題のうち、今回は電源電圧に含まれる雑音への対策を紹介します。

本連載では第33回からさまざまな電子回路の基準電圧を生み出すアナログ回路「Band Gap Reference(BGR)」について解説してきました。第33回はBGR回路の基本原理を、第34回には温度変化の悪影響を抑制したBGR回路を設計しました。

これまでの内容でBGR回路はひとまず完成と言いたいところでしたが、実際にはまだ検討すべき項目が残っています。例えば、BGR電圧の応答速度やトランジスタの相対バラツキを考慮した工夫、電源電圧に含まれる雑音への対策などです。今回は、このうちの電源雑音への対策をピックアップし、詳しく説明したいと思います。

AC解析で周波数ごとの雑音耐性を確認

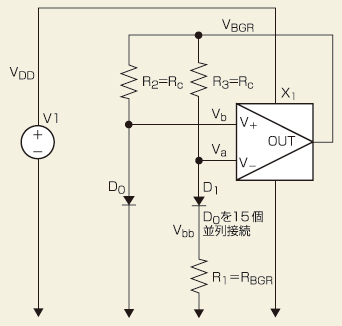

図1は前回(第34回)に完成させたBGR回路です。実際に使うときには、BGR回路を構成するオペアンプの出力(VBGR)を、さまざまな回路の基準電圧に使います。

図1 これまでに設計してきたBand Gap Reference(BGR)回路 本連載では、第33回と第34回でBGR回路の設計に取り組んできました。オペアンプの回路構成は、第34回の図4を参照してください。

基準電圧ですから、できるだけ雑音の少ないきれいな電圧を供給する必要があります。図1の電源電圧(VDD)に雑音が載っていなければいいのですが、そう甘くはありません。VDDには、雑音やリップル電圧などが重畳されているというのが世の常です。従って、BGR回路はVDDに含まれた雑音を消すという役目を担う必要があるのです。

それでは早速、VDDの雑音を除去する回路を考えてみましょう。BGR回路がどれだけVDDの雑音を除去しているのかを調べるには、図1の電源V1を信号源と設定し、AC解析(小信号解析)をするのが分かりやすい方法です。

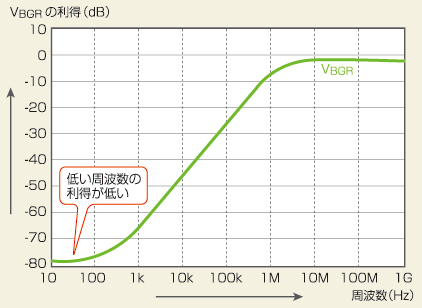

図2にAC解析の結果を示しました。このグラフから、VDDに含まれた低い周波数(例えば、10Hz)の雑音は−80dB、すなわち1/10000に抑制されて現れてきます。つまり、低い周波数の雑音*1)はかなり小さくなるということが分かります。

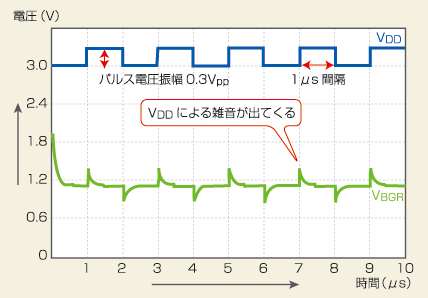

それでは、高い周波数の雑音はどうなるかというと、周波数が高くなるほど利得が上昇しますので、雑音を除去できなくなってしまいます。例えば、電源電圧にパルス状の雑音が載ったときの回路動作を過渡解析で調べてみると、VDD(入力)が変化したときだけ、VBGRに雑音が出てきます(図3)。この雑音は、VDDの変化に対してBGR回路が応答できていないために発生します。従って、BGR回路の応答を速くすることで解決できるはずです。

位相補償用コンデンサの容量を下げる

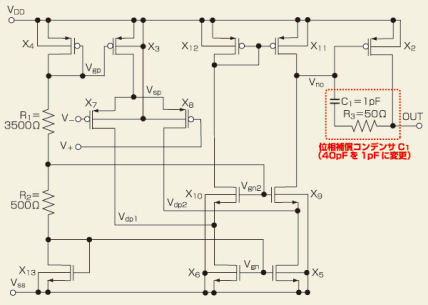

どのようにすれば、BGR回路の応答を速くできるでしょうか? 図4を見てください。図1のオペアンプの部分をひもといた回路です。このオペアンプの位相補償用コンデンサを小さくすることで、応答速度を高められます。位相補償コンデンサの仕組みは、本連載の第20回「差動対がオペアンプに変身(5)〜コンデンサを追加して位相補償〜」を参照してください。

ただし、位相補償用コンデンサを小さくすると応答速度は高くなりますが、一方でオペアンプが発振しやすくなるので注意が必要です。図1をよく見ると、BGR回路はVaとVbが等しくなるようにVBGRを制御する負帰還回路であることが分かります。従って、位相補償用コンデンサを小さくし、位相余裕がなくなってしまうと発振するのです。言い換えると位相補償用コンデンサは、負帰還の動作速度をゆっくりにして、回路を安定荷動作させる役目を持っているので、コンデンサの値を小さくするということは回路が不安定になるということです。

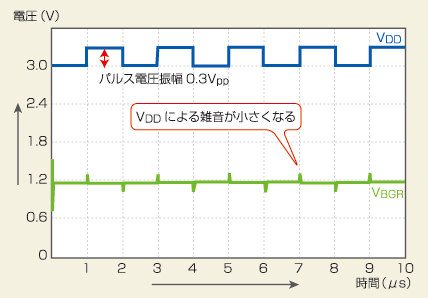

図5に、図4の位相補償コンデンサを40pFから1pFに変更したときの過渡解析の結果を示しました。図3に現れていた電源雑音の悪影響がほとんど抑えられていることが分かります。

Copyright © ITmedia, Inc. All Rights Reserved.