“シリコンコンバージェンス”へ、3次元FPGAの取り組みをAlteraが説明:プログラマブルロジック FPGA

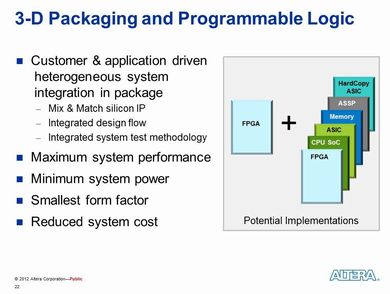

これまで個別のデバイスとして存在していたFPGAとASIC、ASSP、DSP、プロセッサなどのシリコンチップをアプリケーションの要件に応じて組み合わせ、3次元技術で単一のパッケージに統合する。Alteraはこれで、柔軟性と消費電力当たりの性能がともに高いコンピューティングデバイスの実現を目指す。

「3次元FPGAが、“シリコンコンバージェンス”時代の幕を開く」――FPGA大手ベンダーのAltera(アルテラ)は、半導体関連企業の首脳陣が集う報道関係者向けイベント「Globalpress Electronics Summit 2012」(米国カリフォルニア州のサンタクルーズで2012年4月23日〜26日に開催)で講演し、3次元パッケージ技術を適用したFPGAの展望と同社の取り組みについて説明した。同社が言う“シリコンコンバージェンス”とは、これまで個別のデバイスとして存在していたFPGAとASIC、ASSP、DSP、マイクロプロセッサなどの異種の(ヘテロジニアスな)シリコンチップを統合することで、プログラムによって機能を再構成できる高い柔軟性を備えつつ、消費電力当たりの処理性能も高いコンピューティングデバイスを実現することを指す。

AlteraのJeff Waters氏 Senior Vice President&General Manager, Military, Industrial and Computing Divisionを務める。

講演に立ったのは、同社Senior Vice President&General Manager, Military, Industrial and Computing Divisionを務めるJeff Waters氏である。同氏は、このシリコンコンバージェンスを可能にする中核技術として、3次元パッケージを挙げた。「3次元技術を適用すれば、当社のFPGAとASICやメモリ、ASSP、DSP、マイクロプロセッサのベアチップ(ダイ)を組み合わせたり、場合によっては他社のFPGAのダイを組み合わせたりして、単一のパッケージに統合できる。それにより、消費電力とサイズを最小限に抑えつつシステム全体の性能を高めるとともに、部品コストを引き下げることが可能になる」(同氏)。

ライバルとは狙いも実現手法も異なる

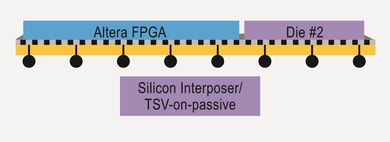

Alteraが現在開発に取り組んでいる3次元パッケージは、シリコン材料を使った支持基板(インターポーザ)の上にFPGAなどの複数のダイを並べて実装し、単一のパッケージに封止した構造をとる。各ダイは、このシリコンインターポーザを介して信号をやりとりしたり、パッケージの端子に接続したりする仕組みだ。複数のダイを縦方向に積層して実装する3次元技術と区別して、「2.5次元」と表現することもできるだろう。

同様のシリコンインターポーザを使う2.5次元パッケージとしては、FPGAの競合ベンダーであるXilinx(ザイリンクス)が「スタックド シリコン インターコネクト」と呼んで発表している。Xilinxは既にこの技術を28nm世代の最新FPGAに適用しており、エンジニアリングサンプル品を出荷済みである。ただし同社は、現時点では同一種のFPGAダイを複数枚組み合わせるホモジニアスな構成を採用し、単一ダイでは実現できない大規模のロジックセルを提供することに主眼を置く。

これに対しAlteraは、前述の通りヘテロジニアス構成を想定しており、狙いに違いがある。「我々にとって最大の市場である通信分野の顧客は、当社が(シングルダイ品で)提供しているFPGAの最大規模品でロジックセルの数は足りるとしている。確かに、ASICプロトタイピングなど一部の市場では、それを超える(シングルダイ品では実現できない)もっと多くのロジックセルが求められる。ただ、そうした市場の規模はあまり大きくない。それよりも、例えばFPGAダイとメモリダイを組み合わせてワンパッケージ化すれば、より規模の大きな市場の要求に応えられる」(Waters氏)。

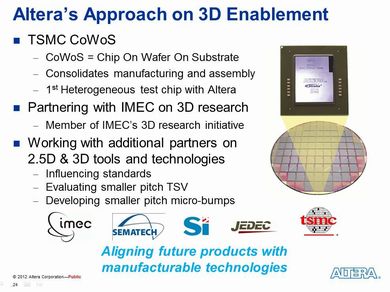

この他に同氏は、2.5次元パッケージの実現方法の違いについても説明した。シリコンインターポーザを使う点や、最終的な2.5次元構造については両社ともに基本的には同じだが、組み立て工程は大きく異なる。Alteraは、同社がFPGAチップの製造を委託している半導体ファウンダリ最大手TSMCの「CoWoS(Chip on Wafer on Substrate)」技術を採用する。これは、インターポーザ用のシリコンウエハーに配線を作り込んだ後、ダイシング(切断)して個片化する前の段階で、ウエハー上の各インターポーザの領域に複数のベアチップをボンディング(接合)し、その後でダイシングするという手法だ。

これに対しXilinxが採用するのは、インターポーザの配線を形成したウエハーを先にダイシングし、その後で各インターポーザにベアチップをボンディングするという手法である。これについては、「インターポーザになるウエハーは非常に薄い。そのため、ダイシング後にボンディングの熱処理を施す手法では、基板に歪みが生じやすく、歩留まりの低下を招いてしまう。それは直ちに製品のコストに跳ね返る」(AlteraのWaters氏)と指摘した。ダイシング前のウエハーであれば、熱処理による歪みは生じにくいと説明する。

Alteraは既に、CoWoS技術を適用したヘテロジニアス構成のテスト用デバイスをTSMCと共同で開発済みである。さらに同社は、ベルギーの研究機関であるIMECらと提携し、3次元技術の開発に取り組んでいるという。

関連キーワード

FPGA | アルテラ | シリコン | 3D | ザイリンクス | ウェハ | ASIC | TSMC | 配線 | 28nmプロセス | DSP(Digital Signal Processor) | 100ギガビットイーサネット | プログラマブルロジック(エレクトロニクス)

Copyright © ITmedia, Inc. All Rights Reserved.