「20nm世代は性能と集積度が2倍、消費電力が1/2に」、ザイリンクスが発表:プログラマブルロジック FPGA

FPGA大手のXilinxが、20nm世代の半導体プロセスで製造する次期FPGA「8シリーズ」の製品戦略を発表した。プロセスの微細化に加えて、28nm世代を適用する現行の「7シリーズ」で新たに導入した複数の技術基盤を改良することで、性能と集積度を2倍に高めたり、消費電力を半分に抑えたりすることが可能になるという。

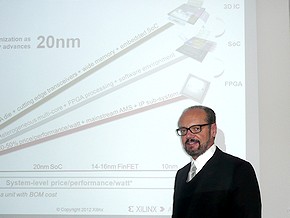

FPGA大手ベンダーである米国のXilinx(ザイリンクス)は2012年11月13日(現地時間)、20nm世代の半導体プロセスで製造する次期FPGAの製品戦略を発表した。28nm世代のプロセスを適用する現行品「Xilinx 7シリーズ」の後継となり、名称は「Xilinx 8シリーズ」になる。半導体プロセスの微細化に加えて、7シリーズで新たに導入した複数の技術基盤を改良することで、「性能が2倍、集積度が1.5〜2倍と高い品種を実現可能だ。あるいは、消費電力を半分に抑えた品種を用意することもできる」(XilinxでVice President, FPGA Platform Marketingを務めるTim Erjavec氏)と主張する。

同社は今回の発表を、「あくまでも製品戦略の発表であり、製品そのものの発表ではない」(同氏)と位置付けており、具体的な品種構成や仕様、供給開始時期といった詳細については、「今後、製品ファミリごとに順次発表していく予定だ」(同氏)として明らかにしていない。ただし、「既に、早期の採用を検討する戦略的に重要な顧客を対象に、製品の定義に取り組んだり、資料の提供を始めたりしている」(同氏)という。

応用市場ごとに3つのタイプをそろえる

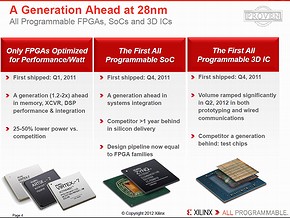

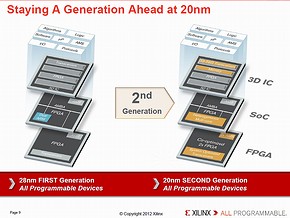

20nmの8シリーズでは、28nm世代の7シリーズと同様に、大きく分けて3つのタイプの製品を用意する。

左の図は、現行の28nm世代で提供している3つのタイプの製品。右の図は、これら3つのタイプについてそれぞれ、28nm世代から20nm世代に移行することで強化される機能を示している。出典:ザイリンクス (クリックで画像を拡大)

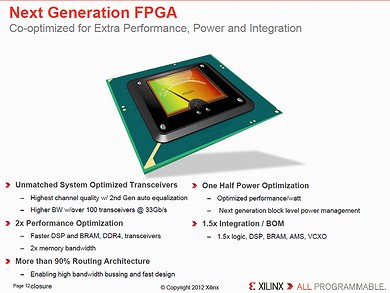

左の図は、現行の28nm世代で提供している3つのタイプの製品。右の図は、これら3つのタイプについてそれぞれ、28nm世代から20nm世代に移行することで強化される機能を示している。出典:ザイリンクス (クリックで画像を拡大)1つ目は、単位消費電力当たりの性能に主眼を置いて最適化した基本的なFPGAである。Xilinxが「性能が2倍、集積度が1.5〜2倍、消費電力が半分」と説明しているのはこのタイプだ。ここで「性能が2倍」とは、DSPブロックや、メモリインタフェース、ブロックRAM、高速シリアルトランシーバなどの各種ハードIP群をそれぞれ高速化することを指す。例えば、メモリインタフェースは28nm世代のDDR3対応からDDR4対応へ高度化し、メモリ帯域幅は2倍に広がるという。高速シリアルトランシーバは、データ伝送速度が28nm世代の12.5Gビット/秒から33Gビット/秒まで向上し、それを100チャネル以上も集積する。

「集積度」については、半導体プロセスの微細化に加えて、同社のFPGA開発ツール群「Vivado Design Suite」に組み込んだアルゴリズムを改良し、「プログラマブルロジック領域の90%以上まで、ユーザーロジックを敷き詰められるようにした」(同氏)という。これによりロジックセルの集積規模が同程度のFPGAなら、28nm世代に比べて1.5倍の規模のユーザーロジックを実装可能だとする。さらに、DSPブロックやブロックRAM、アナログ信号処理ブロックといったハードIP群の集積数も増える。従って、品種によって「1.5〜2倍の集積度」が得られるというわけだ。

消費電力については、半導体プロセスの微細化に伴って電源電圧を引き下げることで低減できる他、回路ブロックレベルの高度な電源管理を導入することでさらなる低減を進める。それにより、品種によっては「28nm世代品の半分」に抑えられるとしている。

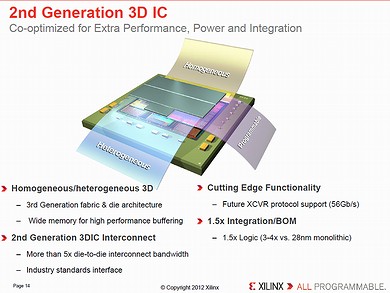

8シリーズで用意する3つのタイプのうち2つ目は、3次元実装技術を適用し、単一のパッケージに複数のチップを収めることで、ロジックセルや高速シリアルトランシーバ、組み込みメモリなどのパッケージ当たりの集積度を大幅に高めたタイプの製品だ(Xilinxの3次元実装技術に関する参考記事)。28nm世代で初めて導入した3次元実装技術を基盤とし、幾つかの拡張を施す。

具体的にはこうだ。28nm世代では、樹脂材料を使うパッケージ基板の上に、Si(シリコン)材料を使った支持基板(インターポーザ)を載せ、その上にFPGAのベアチップ(ダイ)を複数枚、同一平面に並べて実装する構造を採っていた。20nm世代では、インターポーザを改良し、ダイ間をつなぐ信号伝送路の帯域幅を5倍以上に広げるという。さらに、同種のFPGAダイを複数搭載する“ホモジニアス”な構成に加えて、FPGAダイとメモリダイや、FPGAダイと高速シリアルトランシーバダイといった具合に異種のダイを組み合わせて実装する“ヘテロジニアス”な構成にも対応する。高速シリアルトランシーバについては、単一パッケージに56Gビット/秒動作の回路を8チャネル内蔵できるようになるという。28nm世代品では、28Gビット/秒動作の回路を最大で7チャネルまで搭載していた。つまり20nm世代品は高速シリアルトランシーバの総帯域幅が2倍以上に広がることになる。

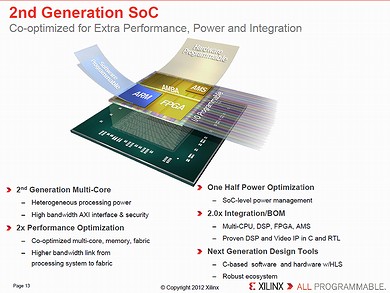

8シリーズで用意する3つのタイプの最後は、FPGAのチップにプロセッサコアをハードIPとして集積したSoC(System on Chip)タイプの派生品である。28nm世代では「Zynq」と呼ぶシリーズをラインアップしていた。28nm世代品は同種のプロセッサコアを複数個集積するマルチコアアーキテクチャをとっていたが、20nm世代品ではヘテロジニアスなプロセッサコアの組み合わせにも対応するという。

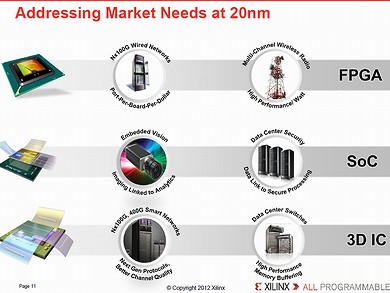

3つのタイプで異なる応用市場を想定

Xilinxは20nm世代品を開発するに当たり、これら3つのタイプそれぞれに異なる応用市場を想定しているという。

基本タイプのFPGAは、ボード当たりのポート数とコストが特に重視される、100Gビット/秒対応の次世代有線ネットワーク機器や、消費電力を低く抑えつつ高い性能を達成することが求められる、多チャネル対応の無線基地局などを狙う。

3次元実装タイプは、次世代プロトコルの処理に対応でき、高いチャネル品質を達成することが目標になる400Gビット/秒対応の有線ネットワーク機器や、高いコンピューティング性能とメモリバッファ性能が要求される、データセンター用スイッチ装置などに向ける。「機器側がFPGAに求める入出力帯域幅が際限なく広がっていくようなハイエンドの応用市場には、半導体プロセスの微細化だけで対応することは不可能だ。3次元実装技術が唯一の解になる」(Erjavec氏)。

SoCタイプは、機器に組み込む画像認識機能や、データセンター向け機器のセキュリティ処理などに使えるとした。

Copyright © ITmedia, Inc. All Rights Reserved.