僒乕僶梡CPU巗応偵挧傓AMD偲ARM偺巚榝乗乗僎乕儉婡偺惉岟儌僨儖傪僒乕僶偱傕丗慻傒崬傒媄弍乮1/2 儁乕僕乯

AMD偼丄ARM偺64價僢僩僐傾傪嵦梡偟偨僒乕僶岦偗CPU乽Seattle乮奐敪僐乕僪僱乕儉乯乿傪丄2014擭戞2巐敿婜偵僒儞僾儖弌壸偡傞偙偲傪柧傜偐偵偟偨丅AMD偼丄ARM僒乕僶巗応偱僔僃傾傪怢偽偡偨傔偵丄摨幮偑僎乕儉婡巗応偱惉岟偟偨偲偒偺儌僨儖傪帩偪崬傕偆偲偟偰偄傞丅偡側傢偪丄僇僗僞儉SoC偺奐敪偩丅Seattle傪斈梡昳偲偟偰巗応偵搳擖偟偨偁偲偼丄偦偆偟偨僇僗僞儉SoC偺奐敪傪恑傔傞梊掕偲偟偰偄傞丅

丂AMD偑ARM僐傾傪嵦梡偟偨僒乕僶岦偗CPU SoC巗応偵嶲擖偡傞寁夋傪柧傜偐偵偟偰偐傜丄栺1擭偑夁偓偨乮娭楢婰帠丗AMD丄ARM儀乕僗偺僒乕僶岦偗SoC巗応偵杮奿嶲擖乯丅嵟弶偵搳擖偡傞僒乕僶岦偗CPU偼丄奐敪僐乕僪僱乕儉乬Seattle乭乮僔傾僩儖乯丅摉弶偺梊掕偱偼2014擭偵巗応搳擖偡傞寁夋偵側偭偰偄偰丄ARM弶偺64價僢僩僐傾偱偁傞Cortex-A57傪嵟戝16僐傾摑崌偡傞偙偲偑柧傜偐偵偝傟偰偄傞丅偝傜偵AMD偼丄慻傒崬傒巗応岦偗偵傕ARM儀乕僗偺SoC傪搳擖偡傞偙偲傪柧傜偐偵偟偰偄偰丄巗応偛偲偵堎側傞惢昳愴棯偱椪傓丅

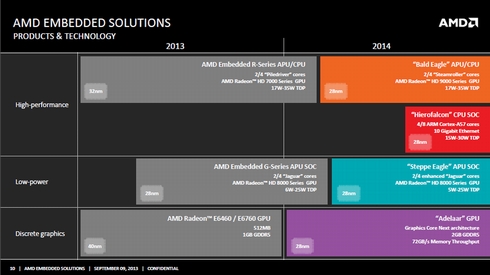

丂AMD偼丄Seattle偺徻嵶傪偁傑傝柧傜偐偵偼偟偰偄側偄丅偟偐偟丄愭偵敪昞偝傟偨慻傒崬傒巗応岦偗儘乕僪儅僢僾偐傜偼丄Seattle偺徻偟偄巔偑尒偊偰偔傞丅摨幮偱慻傒崬傒巗応岦偗價僕僱僗傪摑妵偡傞傾儖儞丒僀僄儞僈乕暃幮挿偼丄崱屻偺惢昳儘乕僪儅僢僾傪岞奐偟丄2014擭偵奐敪僐乕僪僱乕儉乬Hierofalcon乭乮僸僄儘僼傽儖僐儞丗僔儘僴儎僽僒側偳丄僴儎僽僒偺堦庬乯偲屇偽傟傞ARM儀乕僗偺CPU傪丄僱僢僩儚乕僋婡婍傗僨乕僞僙儞僞乕岦偗僗僩儗乕僕側偳偺梡搑偵岦偗偰搳擖偡傞偙偲傪柧傜偐偵偡傞偲偲傕偵丄摨CPU偺僗儁僢僋偵偮偄偰傕丄傛傝徻嵶側巇條傪岞奐偟偨丅

丂偙傟偵傛傟偽丄Hierofalcon偼丄Cortex A-57傪嵟戝8僐傾峔惉偱搵嵹偟偨CPU偱偁傝丄10僊僈價僢僩僀乕僒僱僢僩婡擻傗PCI Express 3.0僀儞僞僼僃乕僗側偳傪摑崌丅偦偺徚旓揹椡偼15乣30W偑僞乕僎僢僩偲側傝丄摦嶌廃攇悢偼嵟戝2GHz偲側傞尒捠偟偩丅僨儏傾儖僠儍僱儖DDR3/DDR4儊儌儕僀儞僞僼僃乕僗偵懳墳偡傞偲偲傕偵丄ECC乮Error Check and Correct乯傪僒億乕僩偡傞偙偲傕柧偐偝傟偨丅AMD偼2014擭戞2巐敿婜偵摨CPU偺僒儞僾儖弌壸傪奐巒偟丄摨擭屻敿偵検嶻傪奐巒偡傞寁夋偩丅

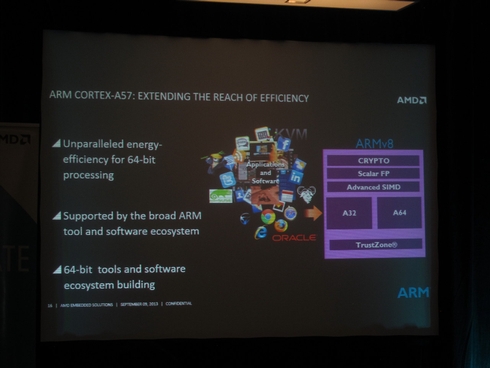

丂Hierofalcon偵嵦梡偝傟傞Cortex A-57偼丄ARM弶偺64價僢僩CPU傾乕僉僥僋僠儍乽ARMv8乿偵懳墳偟丄婛懚偺32價僢僩傾僾儕働乕僔儑儞偲偺屳姺惈傪曐偭偰偄傞丅AMD偼丄ARM偐傜摨CPU僐傾偺儔僀僙儞僗傪庴偗丄儊儌儕僐儞僩儘乕儔側偳帺幮偺IP乮Intellectual Property乯偲摑崌傪壥偨偡丅僀僄儞僈乕暃幮挿偼乽偙偺ARM弶偺64價僢僩CPU僐傾傪丄x86巗応偱弶偺64價僢僩懳墳傪壥偨偟偨AMD偑嵦梡偡傞偙偲偱丄摨幮偺宱尡傪惗偐偟側偑傜丄怴偟偄ARM巗応傪憂憿偱偒傞乿偲傾僺乕儖丅ARM僒僀僪傕丄乽2012擭偵41壄儐僯僢僩傪弌壸偟偨ARM儀乕僗偺慻傒崬傒婡婍巗応偑丄CPU僐傾偺64價僢僩壔偲AMD偲偺僷乕僩僫乕僔僢僾偵傛傝丄偝傜偵奼戝偟偰偄偔偼偢偩乿乮慻傒崬傒巗応岦偗偺儅乕働僥傿儞僌傪扴摉偡傞僔儍乕儕乕儞丒儅儕乕僯暃幮挿乯偲丄婜懸傪婑偣傞丅

丂AMD偱慻傒崬傒價僕僱僗傪扴摉偡傞Kamal Khouri巵偼丄Hierofalcon偲Seattle偼丄婎杮揑偵嫟捠偺敿摫懱僨僓僀儞傪嵦梡偟偰偄傞偑丄僀儞僞乕僐僱僋僩媄弍偱偁傞Freedom Fabric偲偄偭偨僨乕僞僙儞僞乕岦偗SoC偺婡擻側偳偑柍岠偵偝傟偰偄傞偲偄偆尒曽傪帵偡丅摨巵偼丄ARM偺32價僢僩/64價僢僩僴僀僽儕僢僪娐嫬傪惍偊偮偮丄摉柺偼ARM偑僱僢僩儚乕僋傗僗僩儗乕僕岦偗婡婍傪僞乕僎僢僩偲偟丄弴師x86 64價僢僩僔僗僥儉傪嵦梡偟偰偄傞儈儕僞儕乕巗応側偳傊傕暆傪峀偘偰偄偒偨偄峫偊傪帵偡丅

Copyright © ITmedia, Inc. All Rights Reserved.