イマジネーションとして初のMIPSアーキテクチャ「Warrior」をアピール:ET2013

イマジネーションテクノロジーズは、MIPSアーキテクチャの5世代となる32/64ビットCPUコア「Warrior」ファミリを開発した。その第1弾として2013年11月に「P5600」を発表した。競合のCPUコア製品に比べて同じ処理性能であればダイサイズ、消費電力ともに小さいという。

イマジネーションテクノロジーズは、「Embedded Technology 2013/組込み総合技術展(ET2013)」(2013年11月20〜22日、パシフィコ横浜)で、MIPSアーキテクチャの5世代となる32/64ビットCPUコア「Warrior」ファミリをパネル展示した。Warriorの第1弾として2013年11月に「P5600」を発表している。競合のCPUコア製品に比べて同じ処理性能であればダイサイズ、消費電力ともに小さいという。

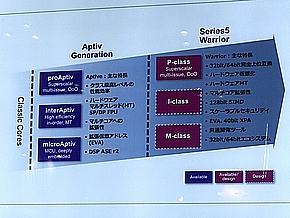

イマジネーションテクノロジーズは、2013年2月にMIPSの買収手続きを完了した。これによって、先端CPUの開発に関わる同社の技術者はほぼ2倍に増強された。製品ファミリも、旧MIPSが「MIPS Aptiv」ファミリを発表していたが、買収完了後には新たなファミリとして「Warrior」を追加した。

Warriorファミリには、32ビット版および64ビット版のCPUコアを用意する予定だ。ハイエンドからミッドレンジ、エントリレベル/マイクロコントローラ用CPUコアをカバーしていく。これらのCPUコアはバイナリレベルでの互換性を保証する。

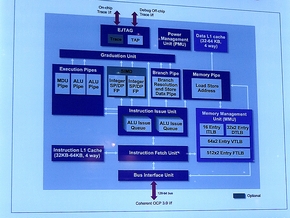

Warriorファミリは、性能や機能によって「Pクラス」、「Iクラス」および「Mクラス」のシリーズ展開を図る計画だ。その第1弾として発表したのが「P5600」である。128ビットのSIMDアーキテクチャを採用し、ハードウェア仮想化をサポートする。演算性能はMHzあたり5CoreMark、3.5DMIPSを達成している。「競合するCPUコア製品に比べてコアあたりの消費電力が小さく、ダイサイズはクラスタレベルで約30%、コアレベルで40%小さい」(説明員)と主張する。

「MIPS Aptiv」ファミリについても拡充を図った。「MIPS Aptiv」ファミリには、ハイエンドの「proAptiv」、マルチスレッド機能を備えた「interAptive」、そしてコンパクトな「microAptive」がある。今回、interAptive製品群にシングルコアバージョンを、microAptive製品群には浮動小数点バージョンを、それぞれ追加した。

今後の取り組みについて、「MIPS CPUコア群は、効率や性能、エリアサイズでクラス最高を実現している。これからはエコシステムの拡充/強化も図っていきたい」(説明員)と話す。

関連キーワード

MIPS | CPU | 電力 | 消費電力 | 64ビット | ET2013 | Imagination Technologies | big.LITTLE処理 | Embedded | マイコン 関連 | 組み込み | Embedded Technology | ハードウェア

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「今すぐ使えるFPGA」、アルテラが運転支援システムなどを提案

「今すぐ使えるFPGA」、アルテラが運転支援システムなどを提案

アルテラは、「今すぐ使えるFPGAソリューション」をテーマに、最新のアルテラSoCやFPGAおよび評価ボードを展示した。パートナー製品も含めて、安価な評価キットやOpenCLを用いて設計が可能なFPGAアクセラレータボード、アルテラSoCを活用した自動車の運転支援システムなどのデモ展示が来場者の注目を集めていた。 ETアワードで「先端テクノロジー賞」受賞、ARMの「big.LITTLE」

ETアワードで「先端テクノロジー賞」受賞、ARMの「big.LITTLE」

ARMは、必要な演算性能によってプロセッサコアを選択して、最適な電力効率で動作させる省電力技術「big.LITTLE」処理を提供している。この省電力技術がETアワード「先端テクノロジー賞」を受賞した。高いピーク性能と低消費電力を両立できる技術として高い評価を得た。 高速通信の評価が容易に、ザイリンクス製FPGAの評価ボードを提案

高速通信の評価が容易に、ザイリンクス製FPGAの評価ボードを提案

ザイリンクスは、販売代理店の東京エレクトロン デバイスやアヴネット・インターニックス、PALTEKなどと協力し、「Zynq-7000 All Programmable SoC」や「Virtex-7 FPGA」といった最新チップの評価ボードなどを展示した。