ギガビットイーサネット対応を5ドル以下で実現、16コア搭載マイコン:プロセッサ/マイコン(2/2 ページ)

XMOS(エックスモス)は、ギガビットイーサネットに対応するマルチコアマイクロコントローラ「xCORE-200」ファミリを開発し、サンプル出荷を始めた。第1弾となる製品は16個のプロセッサコアを内蔵しており、最大2000MIPSの処理性能を実現しながら、量産時の価格は5米ドル以下と安価である。

MCU、DSP、FPGAおよびインタフェース機能を1チップに集積

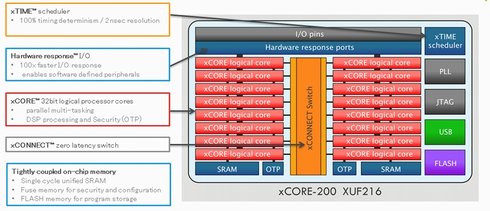

xCORE/xCORE-200ファミリは、組込みシステム開発において、FPGAのような設計の柔軟さと高い性能、およびマイクロコントローラのような低コストでの実装を可能とする製品である。同社がロジカルコアと呼ぶ32ビットRISCプロセッサコアを最大32個搭載し、各コアが独立してそれぞれのタスク処理を行う。このため、「処理の途中で割り込みイベントが発生してもコアごとの処理性能は保証される。GPIOに対しても各コアは均等にアクセスすることができる」(Lippett氏)という。従来、リアルタイムOSが行ってきたスケジューラの機能はハードウェアで実装しており、リアルタイムOSが不要となる。

1つのダイ(タイル)には、基本的に8個のロジカルコアが搭載されている。16コア品であれば、2つのダイで構成する。xCORE-200ファミリの場合、4つのダイを組み合わせて32コア品を実現する。演算性能はダイ当たりの合計値となり、16コア品で2000MIPSの場合、1コア当たり125MIPSの処理能力となる。Lippett氏は、「12コア品で2000MIPSの性能を達成することも可能」という。

プロセッサコア間など内部の回路ブロックを接続するために「xコネクトスイッチ」技術を用いている。一般的なマイクロコントローラのようにメモリを介してデータ伝送を行うのではなく、xコネクトスイッチを介してタイル内外のプロセッサコア同士間で直接通信することができるという。

もう1つの特長が、GPIOやSPI、I2Cなどの各種I/O端子をソフトウェアで自在に設定することができることだ。「ハードウェアレスポンスポート」と呼ぶI/O端子は、ナノ秒単位でタイミングをコントロールすることが可能となっている。

xCORE/xCORE-200ファミリは、これまでは一般的なマイクロコントローラとDSP、CPLD/FPGAおよび複数のインタフェースICなどで構成していた機能を、1個のICに集積することができることから、同等機能を実現する場合に「部品コストを70%削減できる」(Lippett氏)と同社では試算している。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

リアルなクモ型ロボットを制御する10米ドルマイコン「xCORE」

リアルなクモ型ロボットを制御する10米ドルマイコン「xCORE」

東京エレクトロン デバイス(TED)は2014年6月、英国のマイコンメーカーであるXMOS(エックスモス)と販売代理店契約を締結し、子会社のパネトロンを通じ、XMOSのマルチコアマイコン「xCORE」の取り扱いを開始した。多数のモーターをリアルタイム制御できるなどのxCOREの特長を生かし、産業機器や車載機器市場での拡販を行っていく。 グラフィックス処理とボイス制御に対応、HMI用Cortex-M4搭載マイコン

グラフィックス処理とボイス制御に対応、HMI用Cortex-M4搭載マイコン

スパンション(Spansion)は、ARM Cortex-M4コアを搭載したマイコンファミリとして、グラフィックス処理を強化した製品と、ボイスコマンド制御が可能な製品を発表した。 ルネサス、2015年度内にSOTB採用マイコンを製品化へ――消費電力1/10以下、0.4V駆動品も可能に

ルネサス、2015年度内にSOTB採用マイコンを製品化へ――消費電力1/10以下、0.4V駆動品も可能に

ルネサス エレクトロニクスは2015年度(2016年3月期)中にも新型トランジスタプロセス技術「薄型BOX-SOI(SOTB:Silicon-on-Thin-Buried Oxide)」を用いたマイコンを製品化する。同技術を用いることで、0.4Vという超低電圧駆動のマイコンが実現できるという。 ルネサス、車載マイコンで先端プロセスを積極導入――90nmアナログ混載プロセス品を開発中

ルネサス、車載マイコンで先端プロセスを積極導入――90nmアナログ混載プロセス品を開発中

ルネサス エレクトロニクスは2015年1月、90nmプロセスを用いて耐圧数十Vクラスのアナログ回路を混載した車載用フラッシュマイコンを開発中であることを明らかにした。 CypressとSpansion統合――Cypressの名が残り、マイコンはシェア9位か

CypressとSpansion統合――Cypressの名が残り、マイコンはシェア9位か

経営統合することで合意を発表したCypress Semiconductor(サイプレス セミコンダクタ)とSpansion(スパンション)。これにより、マイコン、特に車載マイコンの勢力図に若干の変化が生じる。