連載

ARMから見た7nm CMOS時代のCPU設計(10)〜PVTコーナーの増加がタイミング解析を難しくする:福田昭のデバイス通信(21)(2/2 ページ)

回路の動作周波数などを左右する大きな要因は「PVT」、つまりプロセス(P)、電源電圧(V)、温度(接合温度T)である。動作周波数の代表値や最高値、最低値は、PVTコーナーの数によって決まる。この数は、微細化とともに急増する傾向にあり、タイミング解析がより難しくなっている。

微細化でレイアウト依存効果が強まる

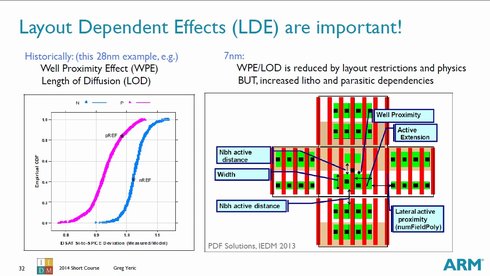

先ほど述べたように動作周波数あるいは遅延時間は、マスクレイアウトの形状によっても変化する。その1つに、レイアウト依存効果(LDE:Layout Dependent Effect)がある。現行の量産世代である28nm世代では、例えばウェル近接効果(WPE:Well Proximity Effect)や拡散長(LOD:Length of Diffusion)などが問題になっている。

研究開発段階にある7nm世代のマスクレイアウト設計では、レイアウト依存効果がさらに強まる。WPEやLODなどの影響はレイアウトの制約によって減少するものの、リソグラフィや寄生素子などの影響が強まると予測される。

(次回に続く)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ムーアの法則、その行方を聞く

ムーアの法則、その行方を聞く

これまで何度となく“終えん説”が唱えられてきたムーアの法則だが、半導体業界は多大な労力でこの法則を維持している。今後、ムーアの法則はどうなっていくのか。業界のキーマンに、ムーアの法則の行方や、ムーアの法則の維持に関わる技術などについて話を聞いた。 「半導体微細化、技術的には7nmも可能」、TSMCの開発責任者がARMイベントで言及

「半導体微細化、技術的には7nmも可能」、TSMCの開発責任者がARMイベントで言及

半導体製造プロセスの微細化は、3次元構造を利用すれば7nmノードも不可能ではないという。だが、問題は技術ではなくコストにある。 シリコンパワーMOSFETの性能改善、素子構造よりもパッケージが効く時代に

シリコンパワーMOSFETの性能改善、素子構造よりもパッケージが効く時代に

SiCやGaNを使う次世代パワー半導体の開発が進んでいるものの、当面は旧来のシリコン材料を用いたパワーMOSFETが広く使われるだろう。ただしシリコン品の性能を高めるには、もはや半導体素子構造の改良では間に合わない。ウエハー処理の後工程となる組み立てプロセスとパッケージ技術の進歩が貢献する。 グラフェン+半導体ポリマーの“ハイブリッド素材”、高性能な有機トランジスタ実現の鍵に

グラフェン+半導体ポリマーの“ハイブリッド素材”、高性能な有機トランジスタ実現の鍵に

スウェーデンの大学とスタンフォード大学が、単層グラフェン上に半導体ポリマーが形成された“ハイブリッド素材”を開発。シリコンに匹敵する性能を持つ有機トランジスタの実現にまた一歩近づいた可能性がある。 塗って乾かすだけの有機半導体でRFIDタグの動作に成功

塗って乾かすだけの有機半導体でRFIDタグの動作に成功

東京大学などのグループは、印刷で製造可能な高性能有機薄膜トランジスタ回路を開発し、電子マネーカードなどで用いられる商用周波数(13.56MHz)での個体識別信号の伝送に「世界で初めて成功した」(東京大学)と発表した。