ムーアの法則、50年をたどる:半導体技術 進化の源(2/2 ページ)

1965年、IntelのGordon Moore(ゴードン・ムーア)氏が雑誌に掲載したトランジスタに関する予見は、「ムーアの法則」として半導体技術の発展の大きな原動力となった。ムーアの法則によってトランジスタがどれほど進化してきたのか。50年を振り返ってみる。

ムーアの法則支えたキーテクノロジー

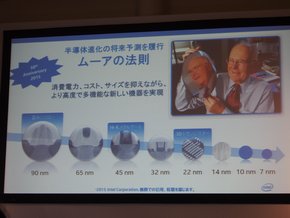

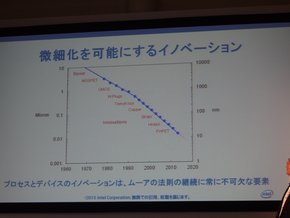

順調に微細化が進んでいたトランジスタも、2000年ごろ、120nm/130nmプロセス付近を境に、単にプロセスルールを微細化するだけでは性能の向上が図れなくなっていった。性能を向上させつつ、低消費電力化や低コスト化も実現するために、Intelは要所要所で新しい技術を導入してきた。90nmプロセスでは歪みシリコンを採用、45nmプロセスではゲート酸化膜を高誘電率/金属ゲート(HKMG:High-k/Metal Gate)に置き換え、22nmプロセスでは3次元構造を適用した。こうした技術が、ムーアの法則に沿った微細化を支えてきたのである。阿部氏は、「つまり今後の10nm、7nmなどでも、何かしらの新しい技術を導入するということだ」と話している。

7nm、5nm……微細化は続くも課題は山積み

何度も「限界説」が唱えられてきたムーアの法則だが、トランジスタの微細化はまだ続いている。Intelは現在、10nmプロセスを開発中で、7nm、5nmの研究にも取り組んでいる。だが、阿部氏は「課題は山積みだ」と話す。「まずは露光装置だ。EUV(極端紫外線)露光装置の登場を、Intelに限らず業界全体が待ち望んでいる。EUV露光技術(の開発)は、日本の存在感も高い分野だ。ただ、Intelでは、7nmプロセスについてはEUVを使わなくても実現できる方法を考えている」(阿部氏)。

また、CMOSトランジスタとは異なる動作原理を用いる「Beyond CMOS」や、3次元トランジスタ、新たなパッケージング技術も、10nm以降を実現する鍵になるという。同氏は、「Intelだけでは、フロントエンドでもバックエンドでも何もできない状態になっていて、パートナーとの協業が欠かせなくなっている。協業するケースが、昔とは桁違いに増えた」と述べている。阿部氏は、「10nmプロセスについては、従来のIntelのルールに従って実現できるのではないかと感じている」と話した。

なお、インテルは2015年夏、ムーアの法則50周年に合わせ、プロセッサの技術などを紹介する展示を科学技術館(東京都千代田区北の丸公園)で行う。若い世代に向けて、コンピュータへ科学への興味喚起を狙う。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「ムーアの法則は間もなく終えんを迎える」、BroadcomのCTOが語る

「ムーアの法則は間もなく終えんを迎える」、BroadcomのCTOが語る

BroadcomのCTO(最高技術責任者)が、「ムーアの法則はあと15年ほどで終えんを迎える。半導体プロセスの微細化は、5nm以降はほぼ進歩しない」という見解を示した。 ムーアの法則は5nmに壁、民生用LSIは28nmで様子見を

ムーアの法則は5nmに壁、民生用LSIは28nmで様子見を

ムーアの法則についての見解を数多く述べているBroadcomのCTO、Henry Samueli氏。微細化技術の今後や、IoT市場の動向、同社のベースバンド事業撤退などについて、話を聞いた。 ムーアの法則、その行方を聞く

ムーアの法則、その行方を聞く

これまで何度となく“終えん説”が唱えられてきたムーアの法則だが、半導体業界は多大な労力でこの法則を維持している。今後、ムーアの法則はどうなっていくのか。業界のキーマンに、ムーアの法則の行方や、ムーアの法則の維持に関わる技術などについて話を聞いた。 SoC設計者が“ポスト・ムーアの法則時代”を生き抜く術

SoC設計者が“ポスト・ムーアの法則時代”を生き抜く術

チップ設計者に「タダ飯」をごちそうしてくれた“ムーアの法則”がなくなろうとしている。これからチップ設計者が生きていくには性能向上と消費電力低減を実現する革新的方法を自ら生み出していくしかない。 終えん間近のムーアの法則、“ポストCMOS”の技術を模索へ

終えん間近のムーアの法則、“ポストCMOS”の技術を模索へ

米国で開催されたシンポジウム「IEEE Technology Time Machine(TTM)2014」では、“ポストCMOS”の技術について議論が交わされた。注目されているのは、量子コンピュータ、ビッグデータ、カーボンナノチューブ、人間の脳(シナプス)をまねた技術などである。