楢嵹

僨僶僀僗媄弍偺拲栚榑暥 乣7nm埲崀傪慱偆崅堏摦搙僩儔儞僕僗僞丗VLSI僔儞億僕僂儉 2015 僾儗價儏乕乮2乯乮4/4 儁乕僕乯

崱夞偼丄儊儌儕暘栰丄愭抂CMOS暘栰丄旕僔儕僐儞暘栰偵偍偗傞嵦戰榑暥偺奣梫傪徯夘偡傞丅掞峈曄壔儊儌儕乮ReRAM乯傗3師尦廲宆峔憿偺憡曄壔儊儌儕乮PCM乯偵娭偡傞榑暥偺懠丄GaN傗SiGe丄InGaAs側偳丄師悽戙偺崅堏摦搙偺壔崌暔敿摫懱傪梡偄偨僩儔儞僕僗僞偵娭偡傞媄弍榑暥偺奣梫偑徯夘偝傟偨丅

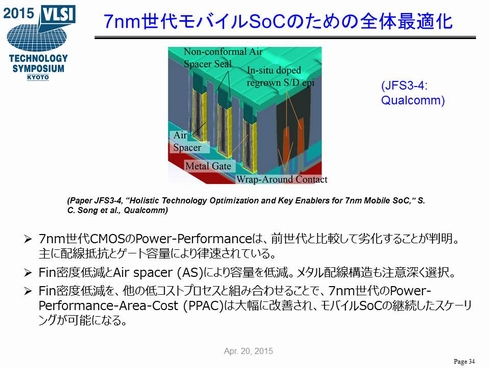

7nm悽戙偺儌僶僀儖SoC岦偗慡懱嵟揔壔媄弍

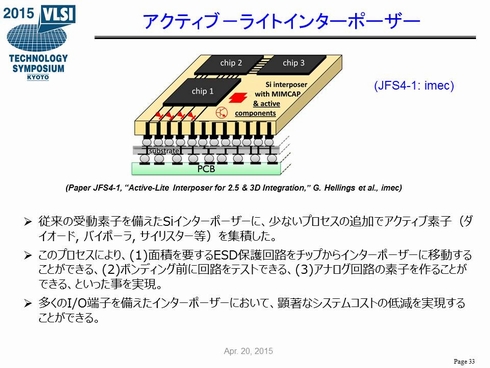

丂偦傟偐傜丄僔儕僐儞偺僀儞僞乕億乕僓偵傾僋僥傿僽慺巕傪宍惉偡傞媄弍偺奐敪惉壥傪徯夘偟偨丅敪昞幰偼imec丅2.5師尦偁傞偄偼3師尦偺僔儕僐儞僟僀愊憌儌僕儏乕儖岦偗偱偁傞丅儅僗僋悢偺彮側偄僾儘僙僗偱丄僔儕僐儞偺僀儞僞乕億乕僓偵僟僀僆乕僪傗僶僀億乕儔丒僩儔儞僕僗僞側偳偺傾僋僥傿僽慺巕傪宍惉偡傞丅ESD曐岇夞楬傗僥僗僩抂巕夞楬丄傾僫儘僌夞楬傪宍惉偡傞偙偲偱丄僔儕僐儞僟僀懁偺僐僗僩傪嶍尭偡傞丅

丂嵟屻偵徯夘偟偨偺偼丄7nm悽戙偺儌僶僀儖SoC岦偗慡懱嵟揔壔媄弍偱偁傞丅敪昞幰偼Qualcomm丅7nm悽戙偱偼丄攝慄掞峈偲僎乕僩梕検偺憹壛偵傛偭偰CMOS僨僶僀僗偺懍搙懳徚旓揹椡偺惈擻偑岦忋偟側偔側傞丅偦偙偱FinFET偺僼傿儞枾搙傪掅尭偡傞丄FinFET偺懁暻愨墢枌傪僄傾僊儍僢僾偵曄峏偡傞偲偄偭偨岺晇偱梕検偺憹壛傪梷偊傞丅攝慄偵娭偟偰偼攝慄宱楬傗奒憌峔憿側偳傪拲堄怺偔挷惍偟丄攝慄掞峈偺憹壛傪旔偗傞丅偙偆偄偭偨岺晇側偳偵傛偭偰7nm悽戙偺儌僶僀儖SoC偱傕僗働乕儕儞僌傪壜擻偵偡傞丅

乮師夞偵懕偔乯

Copyright © ITmedia, Inc. All Rights Reserved.

娭楢婰帠

14nm SoC傗怴婯儊儌儕側偳偺尋媶惉壥傪敪昞傊乗乗擔杮偺嵦戰榑暥悢偼暷崙偵師偖寁27審

14nm SoC傗怴婯儊儌儕側偳偺尋媶惉壥傪敪昞傊乗乗擔杮偺嵦戰榑暥悢偼暷崙偵師偖寁27審

2015擭6寧偵奐嵜偝傟傞崙嵺妛夛乽VLSI Technology僔儞億僕僂儉乿偲乽VLSI Circuits僔儞億僕僂儉乿偺奣梫偑柧傜偐偵側偭偨丅IoT乮儌僲偺僀儞僞乕僱僢僩乯幮夛偺幚尰偵岦偗偨LSI偺僨僶僀僗媄弍偲夞楬媄弍側偳偵娭偟偰丄嵟愭抂偺尋媶惉壥偑斺業偝傟傞梊掕偱偁傞丅 儉乕傾偺朄懃丄50擭傪偨偳傞

儉乕傾偺朄懃丄50擭傪偨偳傞

1965擭丄Intel偺Gordon Moore乮僑乕僪儞丒儉乕傾乯巵偑嶨帍偵宖嵹偟偨僩儔儞僕僗僞偵娭偡傞梊尒偼丄乽儉乕傾偺朄懃乿偲偟偰敿摫懱媄弍偺敪揥偺戝偒側尨摦椡偲側偭偨丅儉乕傾偺朄懃偵傛偭偰僩儔儞僕僗僞偑偳傟傎偳恑壔偟偰偒偨偺偐丅50擭傪怳傝曉偭偰傒傞丅 TSMC丄10nm僾儘僙僗偱偼僀儞僥儖偲偺媄弍嵎側偔側傞

TSMC丄10nm僾儘僙僗偱偼僀儞僥儖偲偺媄弍嵎側偔側傞

TSMC偼丄10nm僾儘僙僗傪揔梡偟偨僠僢僾偺惢憿傪2017擭偵奐巒偡傞丅摨幮偼乽僀儞僥儖偺10nm僠僢僾偲摨摍儗儀儖偺惈擻傪幚尰偱偒傞偲尒偰偄傞丅10nm僾儘僙僗偱丄僀儞僥儖偲偺媄弍揑側僊儍僢僾傪杽傔傜傟傞偩傠偆乿偲弎傋偰偄傞丅 TSMC丄2015擭敿偽偵16nm FinFET偺検嶻奐巒傊

TSMC丄2015擭敿偽偵16nm FinFET偺検嶻奐巒傊

TSMC偼丄16nm僾儘僙僗埲崀偺儘乕僪儅僢僾傪柧傜偐偵偟偨丅傑偢偼2015擭敿偽偵丄16nm FinFET亄傪揔梡偟偨僠僢僾偺検嶻傪奐巒偡傞丅2016擭偵偼丄10nm僠僢僾偺惗嶻岺応偺寶愝偵傕拝庤偡傞丅 Samsung偑14nm悽戙偺FinFET傪揥帵丄巇條偼柧偐偝偢

Samsung偑14nm悽戙偺FinFET傪揥帵丄巇條偼柧偐偝偢

Samsung Electronics乮僒儉僗儞揹巕乯偑丄ARM庡嵜偺僀儀儞僩偱14nm悽戙偺FinFET僾儘僙僗媄弍傪揔梡偟偨僠僢僾傪敪昞偟偨丅TSMC傕偦偺捈慜偵16nm FinFET僾儘僙僗傪梡偄偨ARM乽Cortex-A57乿偺専徹傪峴偭偰偄傞偑丄偁傞愱栧壠偼丄16/14nm FinFET偺惈擻偵偮偄偰偼丄Samsung偲TSMC偼屳妏偩偲傒偰偄傞丅