CPUコアごとにソフトウェアの消費電力を解析:ソフトウェア処理に要する電力消費を見える化

富士通研究所は、CPUコアごとにソフトウェア処理で消費される電力を算出する技術を開発した。これにより、省電力のプログラミングを実現することができる。従来のハードウェアによる低電力技術と組み合わせ、サーバシステム全体のさらなる低消費電力化や高性能化が可能となる。

富士通研究所は2015年7月、CPUコアごとにソフトウェア処理で消費される電力を算出する技術を開発したことを発表した。これにより、省電力のプログラミングを実現することができる。サーバシステム全体の低消費電力化や高性能化が可能となる。同社は2016年度の実用化を目指している。

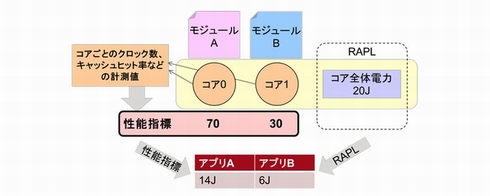

Intel製CPUを搭載したサーバでは、電力制御のためのRAPL(Running Average Power Limit)機構を利用して、CPU全体の消費電力を把握することができる。しかし、各CPUコア上で実行されるソフトウェアの消費電力を計測/分析することまではできなかった。

富士通研究所は、Intel製CPUを搭載したサーバ上で、CPUコアごとに取得できるクロック数やキャッシュヒット率などの情報を活用して、プログラムのモジュール単位に消費電力を推定することができる電力解析技術を開発した。CPUコアごとに算出した性能指数に従って、CPUの消費電力を各コアに配分することで、モジュール単位により詳細なソフトウェアの消費電力を把握することが可能となる。

性能指数に用いるCPUコアごとの計算値を、クロック数やキャッシュヒット率など数種類に絞ることで、取得する時間を1msで行うことができ、電力情報を算出するためのオーバーヘッドも全体の1%程度に抑えることができるという。

世界トップレベルの処理速度を実現しているスパコンの消費電力量は約18MWといわれている。また、日本のデータセンタの消費電力量は、年平均77.2億kWhとの報告もあり、消費電力の節減が大きな課題となっている。

富士通研究所では、今回開発した「ソフトウェアにおける電力消費の見える化」技術により、省電力プログラミングを実現し、サーバ全体の電力消費削減や、プログラムの高性能化につながるとみている。今後はソフトウェアによる消費電力削減の実証を重ねつつ、富士通のデータセンタへの技術適用なども検討し、2016年度には実用化したい考えだ。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

部屋を丸ごとデジタル化? 富士通のUI技術を体験

部屋を丸ごとデジタル化? 富士通のUI技術を体験

富士通研究所、富士通デザイン、富士通ソーシアルサイエンスラボラトリは2015年7月、部屋全体をデジタル化するUI技術を検証する実証実験を行うと発表した。複数の人の端末の画面を同じ空間で共有、操作でき、会議やワークショップなどで効率的な情報共有とコミュニケーションの活性化が可能になるという。説明会では同技術を活用したデモが行われたので、その様子を紹介する。 自動車や次世代医療分野で新ビジネス創出へ、富士通研が応用研究に注力

自動車や次世代医療分野で新ビジネス創出へ、富士通研が応用研究に注力

富士通研究所は、研究開発戦略説明会を開催した。「ハイパーコネクテッドクラウド」を支えるコア技術の開発を加速するため、新たに「システム技術研究所」や「知識情報処理研究所」、「応用研究センター」を設置した。 “あえて低解像度”の映像で人の流れを認識、プライバシー保護で

“あえて低解像度”の映像で人の流れを認識、プライバシー保護で

富士通研究所は、監視カメラで撮影した低解像度の映像から、人の流れを認識することができる技術を開発した。この技術を活用することで、個人のプライバシーを侵害せずに、街中や施設内などにおいて、避難誘導や混雑解消などを容易に行うことが可能となる。 LTE-Advancedの無線基地局配置を最適化する設計技術を開発――富士通研

LTE-Advancedの無線基地局配置を最適化する設計技術を開発――富士通研

富士通研究所は、LTE-Advancedに対応する無線基地局を、最適に配置するための設計技術を開発した。通信速度をより高速化することができ、従来と同等の通信速度を確保するのであれば、基地局数を約3割削減することが可能となる。