連載

ASMLがEUVリソグラフィ開発の最新状況を公表(1)〜ArF液浸の限界:SEMICON West 2015リポート(4)(2/2 ページ)

今回は、コストとパターン形成の2点について、ArF液浸とEUV(極端紫外線)リソグラフィを比べてみよう。ArF液浸では、10nm世代になるとステップ数と重ね合わせ回数が破壊的な数値に達してしまう。これがコストの大幅な上昇を招く。さらに、ArF液浸とEUVでは、10nm世代の配線パターンにも大きな差が出てくる。

10nm世代でもEUVがArF液浸に比べて良好なパターンを形成

ArF液浸リソグラフィとEUVリソグラフィを比較すると、重要な違いがもう1つ存在する。ニコンの講演でも指摘されていた、レイアウトのパターンとレジスト露光パターンのずれ(EPE:Edge Placement Error)である。

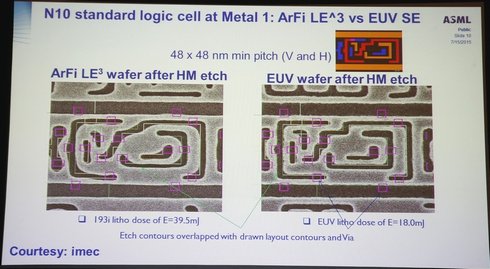

Lercel氏は講演で、ArF液浸のトリプルパターニング(LELELE方式)とEUVのシングルパターニングを第1層金属配線のリソグラフィで比較したスライドを見せていた。縦48nmピッチ×横48nmピッチの最小ピッチで配線パターンを形成した事例である。両者のパターンは明確に違う。EUVのシングルパターニングによる配線パターンが、レイアウトのパターンに近い。ArF液浸のトリプルパターニング(LELELE方式)による配線パターンは、かなり劣る。

この事例のロジック配線は、10nm世代に相当する。10nm世代でも、EUVリソグラフィが良好なパターンを形成しやすい。ArF液浸リソグラフィ(マルチパターニング)は、かなり無理をしていることが分かる。

10nm世代のロジック配線を異なるリソグラフィ技術で形成した結果。左はArF液浸のトリプルパターニング(LELELE方式)で形成したもの。右はEUVのシングルパターニングで形成したもの。EUV露光装置には、ASMLが開発した装置を使用した(クリックで拡大)

(次回に続く)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- ⇒「福田昭のデバイス通信」バックナンバーはこちら

ARMから見た7nm CMOS時代のCPU設計(1)

ARMから見た7nm CMOS時代のCPU設計(1)

ARMにとって「IEDM」は非常に重要だ。この会議で議論されるトランジスタ技術が同社のCPUアーキテクチャの行方を左右するからである。ARMは「IEDM 2014」で、CPU設計とデバイス・プロセス技術の関わりを解説する講義を行った。今回から、その内容を複数回にわたってお届けする。 「20nmプロセスはダブルパターニングがコスト増要因に」、TSMCのCTOが明かす

「20nmプロセスはダブルパターニングがコスト増要因に」、TSMCのCTOが明かす

TSMCは、20nmプロセスの試験生産を2012年第3四半期から開始する。しかし、同プロセスに採用したダブルパターニングによって、28nmプロセスと比べて製造コストが増える見込みだ。 FinFET以降の半導体製造技術はどう進む? IBMの見解

FinFET以降の半導体製造技術はどう進む? IBMの見解

「Common Platform Technology Forum」において、IBMが半導体製造技術の将来展望について発表を行った。液浸リソグラフィによるダブルパターニング技術やFD-SOI技術に加え、カーボンナノチューブ、シリコンフォトニクス、ナノワイヤーなどのキーワードを交えて半導体製造の将来像や課題などが示された。