サーバ間の光通信向け、56Gbps送受信回路を開発:従来と同等の消費電力で、データ通信速度は2倍

富士通研究所とソシオネクストは、サーバ間のデータ通信において、チャネルあたり56Gビット/秒(Gbps)の通信速度を実現する送受信回路を開発した。従来に比べ消費電力は同じで、データ通信速度を2倍にすることが可能となる。

富士通研究所とソシオネクストは2016年2月、サーバ間のデータ通信において、チャネルあたり56Gビット/秒(Gbps)の通信速度を実現する送受信回路を開発したと発表した。消費電力は従来と同じで、データ通信速度を2倍にすることが可能な技術である。

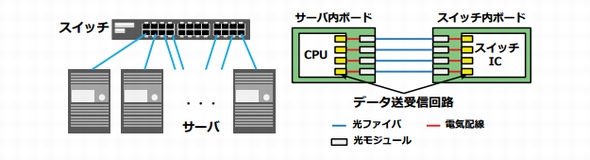

データセンターに設置されたサーバなどの処理性能を向上させるため、サーバ間のデータ通信を高速にする要求が高まっている。このため業界では、消費電力を増やさずに、サーバやスイッチに用いられているICチップと光モジュール間のデータ通信速度を、現行の2倍にするための標準化活動などに取り組んでいる。

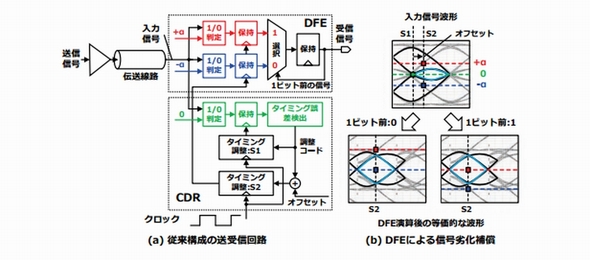

これまでの一般的な送受信回路は、劣化した信号を補償するための回路「DFE(Decision Feedback Equalizer)」ブロックと、入力信号のタイミング誤差を検出するための回路「CDR(Clock and Data Recovery)」ブロックの2つで、送受信回路全体が消費する電力の約3分の2を占めている。このため、通信速度の向上と消費電力の抑制を両立させることが極めて難しかったという。

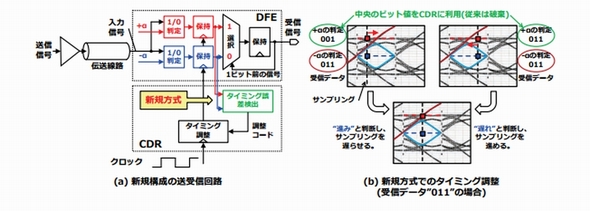

富士通研究所とソシオネクストは、DFE演算後の波形分析を行った。そうしたところ、連続する3ビットの入力信号が「100」または「011」となる時、DFEの2つの判定回路で得られた結果を比較すれば、動作タイミングの「進み」や「遅れ」を検出できることが分かった。この結果に基づいて、連続する3ビットの入力信号が「100」または「011」の時だけタイミングを検出する新たな方式を開発した。

新たに開発したタイミング検出方法を用いると、これまで必要だったCDRの入力信号のタイミング判定回路を削減することができる。その上、DFEとCDRのタイミング調整に用いていたクロック用の配線も不要となり、消費電力を増やさずにデータ通信速度を2倍とする送受信回路を実現した。

現行の28Gbps規格で400Gbpsイーサネットを構築するには、送受信回路がこれまで16個必要であった。これに対して、今回開発した技術を用いると半分の8個で済む。光モジュールの小型化も可能だという。富士通研究所とソシオネクストは、開発した技術について2018年度の実用化を目指す。

今回開発した技術の詳細は、米国サンフランシスコで開催される半導体集積回路技術の国際会議「ISSCC(IEEE International Solid-State Circuits Conference) 2016」(2016年1月31日〜2月4日)で発表する。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

企業論文の採択率回復、日本は2位に、ISSCC概要

企業論文の採択率回復、日本は2位に、ISSCC概要

2016年1月31日より始まる「ISSCC 2016」の概要が明らかとなった。IoE/IoT社会の実現に向けて、デバイス技術やシステム集積化技術の進化は欠かすことができない。特に、電力効率のさらなる改善と高度なセキュリティ技術は一層重要となる。これら最先端の研究成果が発表される。 5Gの携帯電話技術とミリ波通信用周波数生成技術

5Gの携帯電話技術とミリ波通信用周波数生成技術

今回から、2016年1月から2月にかけて米国で開催される半導体関連の国際学会「ISSCC(IEEE International Solid-State Circuits Conference)」を紹介していく。基調講演は、ムーアの法則や5G携帯電話、自動車通信などがテーマになっている。 5Gの通信容量を2倍に、富士通研究所らが開発

5Gの通信容量を2倍に、富士通研究所らが開発

富士通研究開発中心有限公司と富士通研究所は、5G(第5世代移動通信)システム向けに、同一セル内で従来の2倍の通信容量を実現することができる無線通信技術を開発した。 GaNの「最小」ACアダプター、充電時間も1/3に

GaNの「最小」ACアダプター、充電時間も1/3に

富士通研究所は、窒化ガリウム(GaN)高電子移動度トランジスタ(HEMT)パワーデバイスを用いて、モバイル端末などの急速充電を可能にする12W出力の小型ACアダプターを開発したと発表した。