ƒپƒ‚ƒٹپEƒAپ[ƒLƒeƒNƒ`ƒƒ‚جٹî‘bپF•ں“cڈ؛‚جƒfƒoƒCƒX’تگM ARM‚ھŒê‚éپAچإگو’[ƒپƒ‚ƒٹ‚ة‘خ‚·‚éٹْ‘زپi4پjپi1/2 ƒyپ[ƒWپj

چ،‰ٌ‚حپANANDƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹ“oڈêŒم‚جƒپƒ‚ƒٹپEƒAپ[ƒLƒeƒNƒ`ƒƒ‚ًŒ©‚ؤ‚¢‚«‚ب‚ھ‚çپAپuCPU‚جƒپƒ‚ƒٹ‚ة‘خ‚·‚é—v‹پپv‚ًچl‚¦‚ؤ‚¢‚پB

NANDƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹ‚ھگV‚µ‚¢ٹK‘w‚ًگ¶‚فڈo‚µ‚½

پ@چ‘چغ‰ï‹cپuIEDMپv‚جƒVƒ‡پ[ƒgƒRپ[ƒX‚إ‰pچ‘ARM Reserch‚جƒGƒ“ƒWƒjƒARob Aitkenژپ‚ھپAپuSystem Requirements for MemoriesپiƒVƒXƒeƒ€‚ھƒپƒ‚ƒٹ‚ة—v–]‚·‚éژ–•؟پjپv‚ئ‘肵‚ؤچu‰‰‚µ‚½“à—e‚ًڈذ‰î‚·‚éƒVƒٹپ[ƒY‚ج‘و4‰ٌ‚إ‚ ‚éپB

پ@‘O‰ٌ‚©‚ç‚حپAچu‰‰‚ج‘و2ƒpپ[ƒg‚إ‚ ‚éپuCPU‚جƒپƒ‚ƒٹ‚ة‘خ‚·‚é—v‹پپv‚جٹT—v‚ً‚²•ٌچگ‚µ‚ؤ‚¢‚éپB‘O‰ٌ‚حپACPUƒAپ[ƒLƒeƒNƒ`ƒƒ‚ج•د‘J‚ًگU‚è•ش‚é‚ئ‚ئ‚à‚ةپANANDƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹ‚ھ“oڈê‚·‚éˆب‘O‚جƒپƒ‚ƒٹپEƒAپ[ƒLƒeƒNƒ`ƒƒ‚ًگà–¾‚µ‚½پB

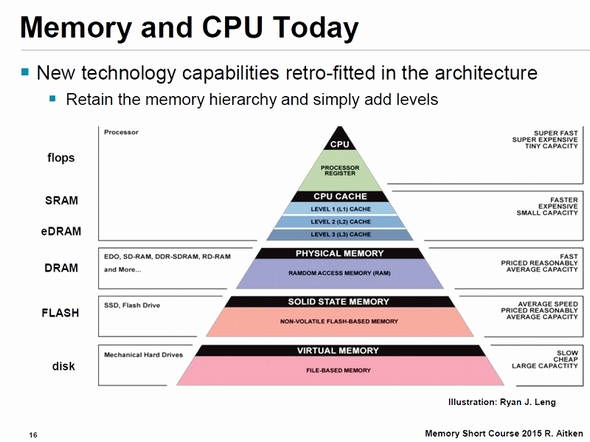

پ@ٹù‚ةڈq‚ׂ½‚و‚¤‚ةپACPU‚ً“‹چع‚µ‚½ƒVƒXƒeƒ€‚جƒپƒ‚ƒٹپEƒAپ[ƒLƒeƒNƒ`ƒƒ‚حپAگ³ژOٹpŒ`‚ ‚é‚¢‚حƒsƒ‰ƒ~ƒbƒhŒ`‚ً‚µ‚½گ}Œ`‚ئپAگ…•½‚بٹK‘w‚ًگ‚’¼•ûŒü‚ةگد‚فڈd‚ث‚½چ\‘¢‚إگà–¾‚·‚邱‚ئ‚ھ‘½‚¢پBNANDƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹ‚ھ”–¾‚³‚ê‚ؤ•پ‹y‚·‚éˆب‘O‚حپAƒsƒ‰ƒ~ƒbƒhگ}Œ`‚ج’¸“_پiچإ‚àچ‚‘¬‚بƒپƒ‚ƒٹپj‚©‚ç’ê•سپiچإ‚à‹L‰¯—e—ت‚ج‘ه‚«‚بƒپƒ‚ƒٹپj‚ةŒü‚©‚ء‚ؤپAپuƒŒƒWƒXƒ^پvپuƒLƒƒƒbƒVƒ…پvپuژه‹L‰¯پvپu‰¼‘z‹L‰¯پiƒXƒgƒŒپ[ƒWپjپv‚جٹK‘w‚إƒپƒ‚ƒٹƒVƒXƒeƒ€‚ًچ\گ¬‚µ‚ؤ‚¢‚½پB

پ@NANDƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹ‚ج”–¾‚ئ•پ‹y‚ة‚و‚ء‚ؤSSDپiSolid State Driveپj‚ة‘م•\‚³‚ê‚éƒtƒ‰ƒbƒVƒ…پEƒXƒgƒŒپ[ƒW‚ھ“oڈꂵپA‹}‘¬‚ةگi‰»‚µ‚ؤ‚¢‚ء‚½پBSSD‚ج‹L‰¯—e—ت‚ح‹}Œƒ‚ة‘‘ه‚µپA‹L‰¯—e—ت“–‚½‚è‚ج’P‰؟‚ح‹}Œƒ‚ة’ل‰؛‚µ‚½پB‚»‚جŒ‹‰تپAƒپƒ‚ƒٹپEƒAپ[ƒLƒeƒNƒ`ƒƒ‚جƒsƒ‰ƒ~ƒbƒhگ}Œ`‚ة‚حپAگV‚µ‚¢ٹK‘w‚ھ‰ء‚ي‚ء‚½پBپuژه‹L‰¯پv‚ئپu‰¼‘zƒپƒ‚ƒٹپv‚جٹش‚ةپASSD‚âUSBƒپƒ‚ƒٹ‚ب‚ا‚جƒtƒ‰ƒbƒVƒ…پEƒXƒgƒŒپ[ƒW‚ة‚و‚éپuŒإ‘جƒپƒ‚ƒٹپiSolid State Memoryپjپv‚جٹK‘w‚ھ“ü‚èژn‚ك‚½پB‚±‚ê‚ھŒ»چف‚جƒپƒ‚ƒٹٹK‘w‚إ‚ ‚éپB

ٹِ”گ«ƒپƒ‚ƒٹ‚ئ•sٹِ”گ«ƒپƒ‚ƒٹ

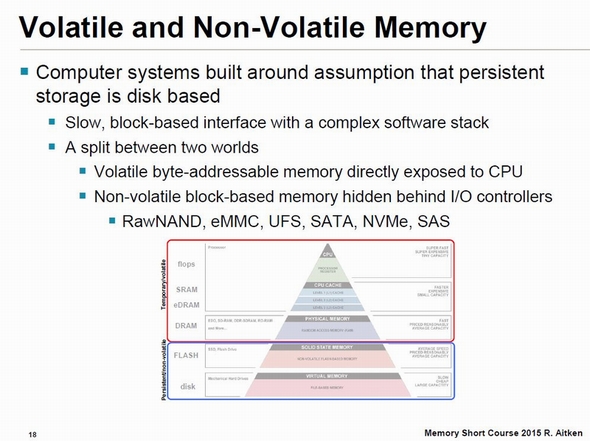

پ@Œ»چف‚جƒپƒ‚ƒٹپEƒAپ[ƒLƒeƒNƒ`ƒƒ‚ح‘ه‚«‚پA2‚آ‚جگ¢ٹE‚ة•ھ‚©‚ê‚ؤ‚¢‚éپB1‚آ‚حپuٹِ”گ«پiVolatileپjپvƒپƒ‚ƒٹ‚جگ¢ٹE‚إ‚ ‚èپA‚à‚¤1‚آ‚حپu•sٹِ”گ«پiNon-Volatileپjپvƒپƒ‚ƒٹ‚جگ¢ٹE‚إ‚ ‚éپB

پ@ٹِ”گ«ƒپƒ‚ƒٹ‚ئ‚حپA“dŒ¹‚ًƒIƒt‚ة‚·‚é‚ئ‹L‰¯“à—e‚ھڈء‚¦‚ؤ‚µ‚ـ‚¤گ«ژ؟‚جƒپƒ‚ƒٹ‚ًژw‚·پBƒپƒ‚ƒٹپEƒAپ[ƒLƒeƒNƒ`ƒƒ‚جƒsƒ‰ƒ~ƒbƒh‚إ‚حڈم•”‚ةˆت’u‚·‚éپBپuƒŒƒWƒXƒ^پv‚©‚çپuژه‹L‰¯پv‚ـ‚إ‚جٹK‘w‚¾پBCPU‚ھƒoƒCƒg’Pˆت‚إ’¼‚ةƒAƒNƒZƒX‰آ”\‚بƒپƒ‚ƒٹ‚جٹK‘w‚إ‚à‚ ‚éپB

پ@•sٹِ”گ«ƒپƒ‚ƒٹ‚ئ‚حپA“dŒ¹‚ًƒIƒt‚ة‚µ‚ؤ‚à‹L‰¯“à—e‚ھˆغژ‚³‚ê‚éگ«ژ؟‚جƒپƒ‚ƒٹ‚ًژw‚·پBƒپƒ‚ƒٹپEƒAپ[ƒLƒeƒNƒ`ƒƒ‚جƒsƒ‰ƒ~ƒbƒh‚إ‚ح‰؛•”‚جˆت’u‚·‚éپB‹ï‘ج“I‚ة‚حپAپuŒإ‘جƒپƒ‚ƒٹپv‚ئپu‰¼‘zƒپƒ‚ƒٹپv‚جٹK‘w‚ھ‘ٹ“–‚·‚éپB

پ@Œإ‘جƒپƒ‚ƒٹ‚ئ‰¼‘zƒپƒ‚ƒٹ‚جٹK‘w‚حپACPU‚ھ’¼‚ةƒAƒNƒZƒX‚إ‚«‚ب‚¢پB‚ـ‚½ƒAƒNƒZƒX’Pˆت‚حƒoƒCƒg’Pˆت‚إ‚ح‚ب‚پA‚à‚ء‚ئ‘ه‚«‚بپuƒuƒچƒbƒNپv‚ئŒؤ‚ش’Pˆت‚ة‚ب‚éپB—ل‚¦‚خ‰¼‘zƒپƒ‚ƒٹ‚جƒfƒoƒCƒX‚إ‚ ‚éHDD‚حپA512ƒoƒCƒg‚ً1Œآ‚جƒuƒچƒbƒN‚ئ‚µ‚ؤˆµ‚¤پB

پ@Œإ‘جƒپƒ‚ƒٹ‚ئ‰¼‘zƒپƒ‚ƒٹ‚إƒfپ[ƒ^‚ج‚â‚è‚ئ‚è‚ًگ§Œن‚·‚é‚ج‚حپA“üڈo—حƒRƒ“ƒgƒچپ[ƒ‰‚إ‚ ‚éپB‚ـ‚¸CPU‚ئ“üڈo—حƒRƒ“ƒgƒچپ[ƒ‰‚ھ’تگM‚µپAژں‚ة“üڈo—حƒRƒ“ƒgƒچپ[ƒ‰‚ھƒپƒ‚ƒٹ‚ةƒfپ[ƒ^‚ًڈ‘‚«چ‚ٌ‚¾‚èپAƒپƒ‚ƒٹ‚©‚çƒfپ[ƒ^‚ً“ا‚فڈo‚µ‚½‚è‚·‚éپBCPU‚©‚猩‚é‚ئپAƒfپ[ƒ^‚ض‚جƒAƒNƒZƒX‚حٹشگع“I‚ة‚ب‚éپB

Copyright © ITmedia, Inc. All Rights Reserved.