ƒپƒ‚ƒٹپEƒAپ[ƒLƒeƒNƒ`ƒƒ‚جٹî‘bپF•ں“cڈ؛‚جƒfƒoƒCƒX’تگM ARM‚ھŒê‚éپAچإگو’[ƒپƒ‚ƒٹ‚ة‘خ‚·‚éٹْ‘زپi4پjپi2/2 ƒyپ[ƒWپj

چ،‰ٌ‚حپANANDƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹ“oڈêŒم‚جƒپƒ‚ƒٹپEƒAپ[ƒLƒeƒNƒ`ƒƒ‚ًŒ©‚ؤ‚¢‚«‚ب‚ھ‚çپAپuCPU‚جƒپƒ‚ƒٹ‚ة‘خ‚·‚é—v‹پپv‚ًچl‚¦‚ؤ‚¢‚پB

ƒAƒhƒŒƒX‚ج•‚ھƒپƒ‚ƒٹ‹َٹش‚ج‘ه‚«‚³‚ًŒˆ‚ك‚é

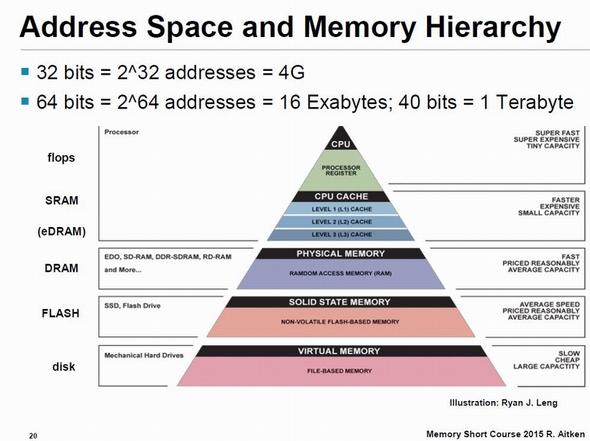

پ@CPU‚ھ’¼‚ةˆµ‚¤ƒپƒ‚ƒٹ‹َٹش‚ج‘ه‚«‚³پi‹L‰¯—e—ت‚ج‘ه‚«‚³پj‚ًŒˆ‚ك‚é‚ج‚حپAƒپƒ‚ƒٹپEƒAƒhƒŒƒX‚ج•‚إ‚ ‚éپB—ل‚¦‚خ32ƒrƒbƒg•‚جƒAƒhƒŒƒXپi32ƒrƒbƒgپEƒAƒhƒŒƒXپj‚جCPU‚ھˆµ‚¤ƒپƒ‚ƒٹ‹َٹش‚ج‘ه‚«‚³‚حپA4GƒoƒCƒgپi2‚ج32ڈوƒoƒCƒgپj‚ة‚ب‚éپBڈ]‚ء‚ؤپA4GƒoƒCƒg‚ً’´‚¦‚éژه‹L‰¯پiƒVƒXƒeƒ€پEƒپƒ‚ƒٹپj‚ً32ƒrƒbƒgCPUƒVƒXƒeƒ€‚ھ“‹چع‚µ‚ؤ‚àپA4GƒoƒCƒg‚ً’´‚¦‚é•”•ھ‚ح’¼گع“I‚ة‚حˆµ‚¦‚ب‚¢پBCPU‚ھˆµ‚¦‚éƒپƒ‚ƒٹ‹َٹش‚ًٹg’£‚·‚éژd‘g‚ف‚ھ•K—v‚ئ‚ب‚éپB

پ@ˆê•ûپA64ƒrƒbƒgپEƒAƒhƒŒƒX‚جCPU‚ھˆµ‚¤ƒپƒ‚ƒٹ‹َٹش‚ج‘ه‚«‚³‚حپA16ƒGƒLƒTƒoƒCƒg‚ة‚à’B‚·‚éپB4GƒoƒCƒg‚ج‚¨‚و‚»40‰”{‚ة‚à‚ب‚é–c‘ه‚ب‘ه‚«‚³‚إ‚ ‚èپAƒپƒ‚ƒٹپEƒAƒhƒŒƒX‚ئ‚µ‚ؤ‚ح‘ه‚«‰ك‚¬‚é‚ئ‚à‚¢‚¦‚éپB

پ@‚»‚±‚إپAŒ»چف‚ج64ƒrƒbƒg‘g‚فچ‚فƒVƒXƒeƒ€‚إ‚حپACPU“à•”‚إƒAƒhƒŒƒX‚ج•‚ً40ƒrƒbƒg‚ة‹·‚ك‚邱‚ئ‚ة‚و‚ء‚ؤƒپƒ‚ƒٹ‹َٹش‚ً1TƒoƒCƒg‚ةڈkڈ¬‚·‚邱‚ئ‚ھ‘½‚¢پB‘g‚فچ‚فƒVƒXƒeƒ€‚إ1TƒoƒCƒg‚ً’´‚¦‚éژه‹L‰¯‚ً“‹چع‚·‚邱‚ئ‚ح“––تپAچl—¶‚·‚é•K—v‚ھ‚ب‚¢‚©‚炾پB

Copyright © ITmedia, Inc. All Rights Reserved.

ٹضکA‹Lژ–

3D XPointپAٹJ”‚©‚çگ»‘¢‚ض

3D XPointپAٹJ”‚©‚çگ»‘¢‚ض

Intel‚ئMicron Technology‚ھٹJ”‚µ‚½پu3D XPointپv‚حپAگ»‘¢‚ج’iٹK‚ض‚ئˆع‚錩چ‚ف‚¾پB—تژY‚ة‚ح12پ`18ƒJŒژ‚©‚©‚é‚ئ‚ف‚ç‚ê‚ؤ‚¢‚éپB‚ـ‚½پA3D XPoint‚إ‚حپAƒJƒ‹ƒRƒQƒiƒCƒhچق—؟‚ئپuOvonyxپvƒXƒCƒbƒ`‚ھژg‚ي‚ê‚ؤ‚¢‚邱‚ئ‚ھ–¾‚ç‚©‚ة‚ب‚ء‚½پB پuƒ€پ[ƒA‚ج–@‘¥‚ًگi‚ك‚é•K—v‚ھ‚ ‚éپvپ\پ\ARM

پuƒ€پ[ƒA‚ج–@‘¥‚ًگi‚ك‚é•K—v‚ھ‚ ‚éپvپ\پ\ARM

2015”N12Œژ7پ`9“ْ‚ةٹJچأ‚³‚ꂽپuIEDM 2015پv‚جٹî’²چu‰‰‚إپAARM‚جƒVƒjƒAƒٹƒTپ[ƒ`ƒƒپ[‚إ‚ ‚éGreg Yericژپ‚حپAپu”¼“±‘جƒ`ƒbƒv‚ج”÷چ׉»‚حˆê’i‚ئچ¢“ï‚ة‚ب‚ء‚ؤ‚¢‚é‚ھپA‚»‚ê‚إ‚àƒ€پ[ƒA‚ج–@‘¥‚ً‘±‚¯‚é•K—v‚ھ‚ ‚éپv‚ئŒê‚ء‚½پB 3D XPoint‚جگ»‘¢ƒvƒچƒZƒX‚حپu20nm‚©‚çƒXƒ^پ[ƒgپv

3D XPoint‚جگ»‘¢ƒvƒچƒZƒX‚حپu20nm‚©‚çƒXƒ^پ[ƒgپv

EE Times Japan‚إ‚ح‚±‚ج‚ظ‚اپAIntel/Micron‚ھ”•\‚µ‚½•sٹِ”گ«ƒپƒ‚ƒٹپu3D XPointپv‚ةٹض‚µ‚ؤ‚ج‹^–â‚ًپA—¼ژذ‚جچL•ٌ’S“–‚ة–â‚¢چ‡‚ي‚¹‚½‚ئ‚±‚ëپAپu20nm‚جƒvƒچƒZƒXƒmپ[ƒh‚إگ»‘¢‚µ‚ؤ‚¢‚éپv‚ئ‚ج‰ٌ“ڑ‚ً“¾‚½پB ژںگ¢‘مƒXƒgƒŒپ[ƒWپA10Œآ‚ج’چ–ع‹Zڈp

ژںگ¢‘مƒXƒgƒŒپ[ƒWپA10Œآ‚ج’چ–ع‹Zڈp

3ژںŒ³DRAM‚ج—تژY‚ھژn‚ـ‚èپA‘ٹ•د‰»ƒپƒ‚ƒٹپiPCMپjپAƒXƒsƒ“’چ“üژ¥‹Cƒپƒ‚ƒٹپiSTT-MRAMپj‚ب‚اژںگ¢‘مƒپƒ‚ƒٹ‚ج‹ZڈpٹJ”‚ھ‚³‚©‚ٌ‚ة‚ب‚ء‚ؤ‚¢‚éپB‚±‚±‚إ‚حپA’چ–ع‚جƒپƒ‚ƒٹ‹Zڈp‚ً10Œآڈذ‰î‚·‚éپB