DRAMについて知っておくべき、4つのこと:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(10)(3/4 ページ)

今回は、DRAMで知っておくべき4つの事実を紹介する。「DRAMの事業規模は巨大であること」「DRAMの性能は常に不足していること」「DRAM開発は傾斜が急になり続ける坂道を登っているようなものであること」「3次元技術はDRAM開発にとって援軍ではあるが救世主ではないこと」の4つだ。

DRAMの性能は常に不足している

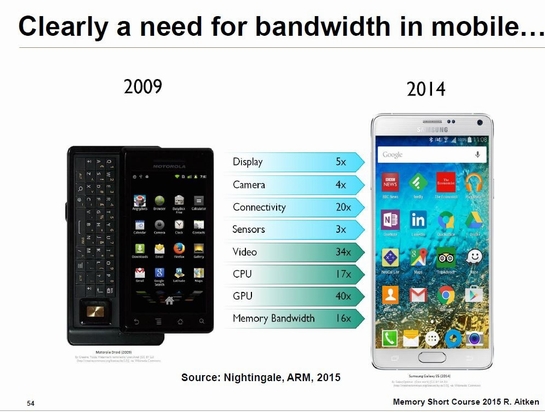

2番目の事実は、DRAMの性能は常に不足しているということだ。具体的には、データ転送速度(帯域幅)が足りない。

例えばモバイル分野である。スマートフォンが必要とするデータ転送速度(帯域幅)は急激に増加しており、DRAMの帯域幅の向上ペースを超えている。2009年と2014年を比べると、メモリに対する帯域幅の要求値は、16倍にも増加した。サーバ分野でも同じような状況が進行している。

限界近くにまでタイミング余裕が縮まる

3番目の事実はDRAM開発が、傾斜が急になり続ける坂道を登っていることだ。次世代のDRAMを開発するたびに傾きはきつくなり、難度が上昇する。近い将来に、坂道の傾斜が登れないくらいの急な角度に達してしまう可能性は少なくない。

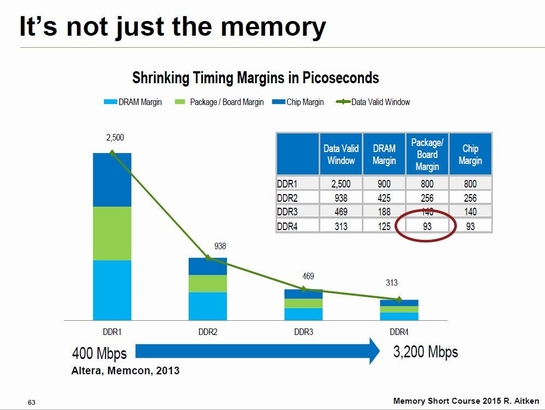

特に厳しいのが、帯域幅の向上である。帯域幅を向上させることは、タイミング余裕の減少を意味する。DDR世代の先駆けであるDDR(1) DRAMの帯域幅は400Mビット/秒だった。このときデータが有効になる期間は2500ps(ピコ秒)ほどあった。ところが第4世代のDDR4 DRAMになると、データが有効になる期間はわずか313psに激減している。

わずか313psのタイミング余裕しか許されない。その中に、DRAMのタイミング余裕とパッケージとボードのタイミング余裕、シリコンチップのタイミング余裕の合計を押し込める必要がある。設計はもちろんのこと、製造も非常に難しい段階に達している。これ以上の高速化、すなわちタイミング余裕の削減が可能かどうかはかなり怪しい。

Copyright © ITmedia, Inc. All Rights Reserved.