SRAMの消費電力と設計の課題:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(14)(1/2 ページ)

今回は、SRAMの消費電力と設計課題について解説する。SRAMの低消費電力化に効果的なのは電源電圧を下げることだが、これには、書き込み不良と読み出しディスターブ不良という問題が付きまとう。

設計ツールのデータで見たSRAMのレイアウト

国際会議「IEDM」のショートコースで英国ARM Reserch社のエンジニアRob Aitken氏が、「System Requirements for Memories(システムがメモリに要望する事柄)」と題して講演した内容を紹介するシリーズの第14回である。

前回は、SRAMの基本要素とレイアウトを解説した。今回は、SRAMの消費電力と設計課題を説明しよう。

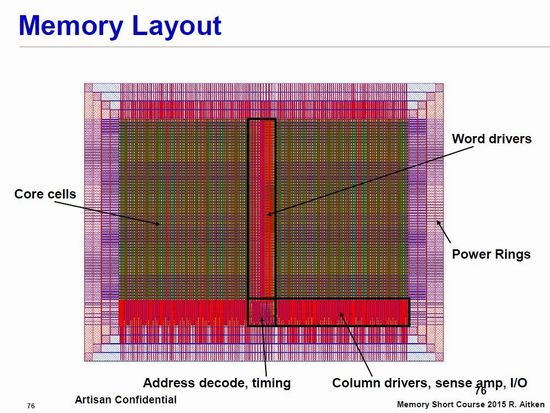

始めに、SRAMシリコンダイの標準的なレイアウトを例示する。前回はレイアウトの概念図を示した。今回は、実際のマスクパターンの元になる、設計ツールのレイアウトデータを採り上げる。

やや横長のシリコンダイは、中央の緑色がかった部分、その周りにある濃い赤色の部分、ダイの周縁部に沿った肌色がかった部分に分かれている。中央の緑色がかった部分がメモリセルアレイである。「コアセル(core cells)」あるいは「コア」とも呼ぶ。濃い赤色の部分は周辺回路(ペリフェラル)である。シリコンダイの中央を縦に貫く部分にワード線ドライバ回路、その下にアドレスデコード回路、その左右にビット線ドライバ(カラムドライバ)回路とセンスアンプ回路、入出力バッファ回路を配置してある。周縁部は電源電圧の分配回路に割り当てられている。リング状にコアとペリフェラルを取り囲むので、「パワーリング(power rings)」とも呼ぶ。

待機時はコア、動作時はカラムが電力を主に消費

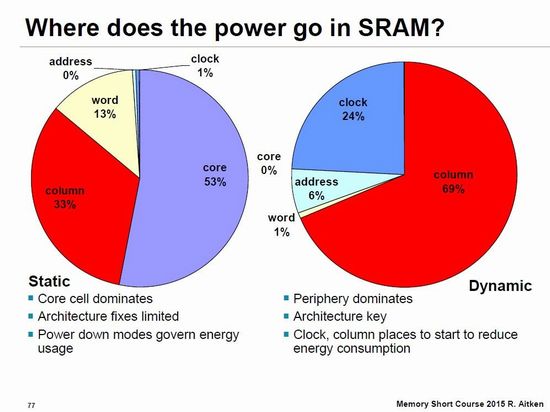

SRAMの消費電力に話題を移そう。SRAMの消費電力を要素別に分類すると、待機時(スタチック状態)と動作時(ダイナミック状態)では電力を消費する要素が大きく違うことが分かる。

待機時消費電力の半分強を占めるのは、コア(メモリセルアレイ)である。次いでカラム部(センスアンプを含む)が3分の1を占める。いずれもトランジスタのリーク電流が電力消費のほとんどを占める。このSRAMはパワーダウンモード(不要なクロック回路を停止したり、不要なドメインの電源をカットするモード)を採用しているので、アドレス回路とクロック回路による消費電力はほぼゼロになる。

動作時消費電力の約7割を占めるのが、カラム部(センスアンプを含む)である。次いでクロック回路が約4分の1を占める。待機時に比べると動作時ははるかに消費電力が大きいので、コアの消費電力は無視できるほどに小さくなる。

Copyright © ITmedia, Inc. All Rights Reserved.