スピン注入型MRAMの不都合な真実:福田昭のストレージ通信(36) 次世代メモリ、STT-MRAMの基礎(14)(2/2 ページ)

STT-MRAMの基礎を解説するシリーズ。最終回となる今回は、磁気トンネル接合(MTJ)を構成する固定層や磁性層に焦点を当てる。スピン注入型MRAMのMTJは、47層もの層で構成されている。これほどの層が必要なのにはきちんとした理由があるのだが、実は同時にそれがSTT-MRAMの弱点にもなっている。

単層では、磁化の固定と電子スピンの偏極を両立しづらい

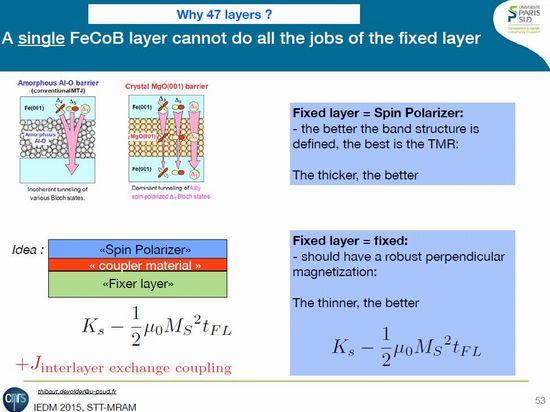

これほどまでに複雑で精密な多層膜を必要とする大きな理由は、固定層が2つの役割を担わなければならないことだ。1つは磁化の固定であり、もう1つは電子スピンの偏極である。磁化の固定については既に説明した。電子スピンの偏極とは、電子スピンの向きを「上向き」あるいは「下向き」にそろえる(偏らせる)ことである。なおここで「上向き」とは、上向きの磁気モーメントを発生するスピンを意味する。このような働きをする素子を「スピン偏極子(spin polarizer)」と呼ぶ。スピン注入による磁化反転を起こす電流の密度を低くするためには、電子スピンが偏極していることが望ましい。

スピン偏極子の効果を高めるには、スピン偏極を起こす層はなるべく厚くしたい。一方で磁化を固定する層は、なるべく薄くしたい。両者は矛盾するため、CoFeBの単層でこれらの条件を両立することは困難である。そこで磁化固定層とスピン偏極子層を分けて成膜し、両者を結合層で接続する、という形で層数を増やして役割りを分担するようになった。

原子層オーダーの超多層膜を低コストで製造できるか

上記の事実を考慮すると、固定層は「固定層」ではなく、「参照層」とでも呼ぶべきだと分かる。「参照層」(多層膜)の中に「固定層」と「スピン偏極子層」がある、という構成である。

磁性体中の磁気モーメントは本質的に動きやすい。このためMTJ素子の設計では、磁気モーメントをしっかりと固定する多層膜の構成にかなりの努力が費やされる。

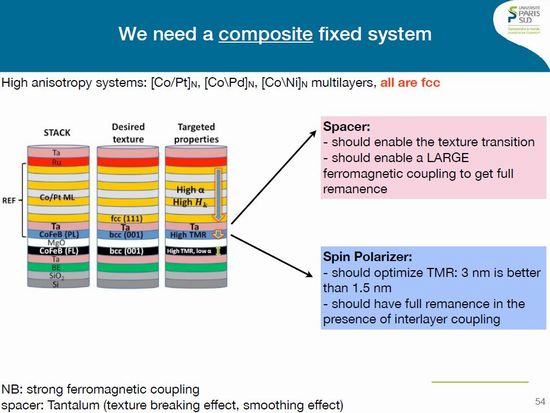

垂直磁気記録方式のMTJ素子を例にとると、いくつもの条件を満足するように工夫がなされている。トップ側を固定層、ボトム側を自由層としてトップ側から層構成を見ていこう。トップ側は多層膜の固定層である。例えばコバルト(Co)と白金(Pt)の多層膜を使う。結晶配向は面心立方の(111)である。磁気異方性係数は非常に大きく、また減衰(ダンピング)定数(α)も大きくする。

多層膜の下にはスピン偏極子層がくる。ここで問題となるのは、スピン偏極子層と固定層では結晶配向が異なることだ。スピン偏極層からボトム側の各層は、結晶配向が体心立方の(001)なのである。そこでタンタル(Ta)のスペーサ層を挟むことで、結晶配向の違いを緩和する。

スピン偏極子層は、電子スピンを偏極させることの他に、磁気抵抗比(MR比)を最大化するという重要な役割りを担う。材料は強磁性体のコバルト鉄ホウ素(CoFeB)合金である。

スピン偏極子層の下はトンネル障壁層である。材料は酸化マグネシウム(MgO)結晶、結晶配向は体心立方の(001)である。トンネル障壁層に続くのは自由層であり、材料はCoFeB合金、結晶配向は体心立方の(001)となる。自由層にはMR比を大きくすることと、ダンピング定数を低くすることが求められる。

上記で説明したようにスピン注入MRAMの最大の弱点は、MTJ素子の異常ともいえる複雑さにある。競合と目される抵抗変化メモリ(ReRAM)と相変化メモリ(PCM)の記憶素子は構造は簡素であり、MTJ素子の複雑さとは比較にならない。このことは、製造コストを下げなければならない半導体メモリでは、重要なファクターだ。

⇒「福田昭のストレージ通信」連載バックナンバー一覧

《次の記事を読む》

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

STT-MRAMの基礎――情報の蓄積に磁気を使う

STT-MRAMの基礎――情報の蓄積に磁気を使う

次世代不揮発メモリの候補の1つに、STT-MRAM(スピン注入磁化反転型磁気メモリ)がある。データの読み書きが高速で、書き換え可能回数も多い。今回から始まるシリーズでは、STT-MRAMの基本動作やSTT-MRAが求められている理由を、「IEDM2015」の講演内容に沿って説明していこう。 “次世代メモリ”の域を出ないFRAM、量産規模を上げて低価格化を

“次世代メモリ”の域を出ないFRAM、量産規模を上げて低価格化を

SRAMやDRAM、EEPROMを置き換えるとして大いに期待されていたFRAMは、量産こそ始っているものの、完全に普及しているとはいえず、いまだに“次世代メモリ”の域を出ない。だが、一定のニーズはある。 FinFETサイズの物理的な限界は?

FinFETサイズの物理的な限界は?

ベルギーで開催された「IMEC Technology Forum(ITF) 2016」では、2.5D(2.5次元)のチップ積層技術や、FinFETのサイズの物理的な限界についても触れられた。 Samsung、2016年内に14nm LPCプロセス提供へ

Samsung、2016年内に14nm LPCプロセス提供へ

Samsung Semiconductorは、第1世代の14nmプロセス技術「14LPP」よりもコストを抑えられる第2世代14nmプロセス技術「14LPC」を2016年中にも提供するとの方針を明らかにした。10nmプロセス技術でも、第1世代の「10LPE」と第2世代の「10LPP」を提供するという。