ルネサス、100Gb向けのパケットヘッダ検索を発表:LLDRAM-IIIとFPGAなどで構成

ルネサス エレクトロニクスは2016年6月、100Gビットトラフィック級の通信機器向けに、パケットヘッダ検索レファレンスデザインの提供を開始した。汎用DRAMメモリで構成した場合と比較して、メモリデバイス数を15分の1、メモリの消費電力を60%削減可能という。

メモリの消費電力を60%削減

ルネサス エレクトロニクス(以下、ルネサス)は2016年6月、100Gビットトラフィック級のルーター、スイッチ、サーバなどの通信機器向けに、パケットヘッダ検索レファレンスデザインの提供を開始した。同レファレンスデザインは、同社の「LLDRAM-III(Low Latency DRAM-III)」と、ザイリンクスのFPGA向け完全一致検索IP、LLDRAM-IIIコントロールIP、開発サポートツールで構成されている。

100Gビットクラスのパケットヘッダ検索機能を、汎用DRAMメモリで構成した場合と比較して、メモリデバイス数を15分の1、メモリの消費電力を60%削減可能という。

「開発期間を約6カ月短縮」

同レファレンスデザインのLLDRAM-IIIは、1秒間に400Mアクセス、57.6Gビット転送を2W以下で動作できる。同社はリリース上で、「同メモリと新開発のアルゴリズムを組み合わせることで、100Gビットトラフィック級で要求される、1秒間に1億5000万回のパケット検索を1個のLLDRAM-IIIで実現できる」と語る。

これにより、メモリデバイス数と消費電力の削減を可能にした。また、メモリ実装面積を90%削減、メモリとFPGA間の配線数も90%減少し、ピン数の少ないFPGAでシステム構成ができるため、コスト低減にも貢献するとしている。

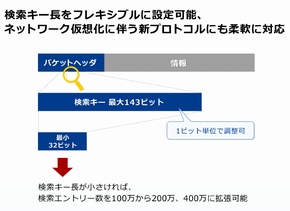

完全一致検索IPは、最大143ビットまで、1ビット単位で任意に変更できる機能を搭載。従来のMACアドレス検索だけでなく、ネットワーク仮想化技術による新たな通信プロトコルにも検索IPを設計変更することなく対応できる。

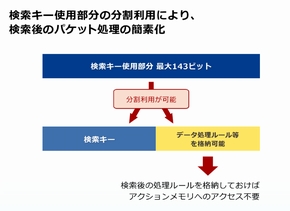

左=最大検索キーを短く設定することで、検索エントリー数を200万、400万へと拡張することも可能/右=検索キーで使用する最大143ビットのビット幅を、検索キーの領域とパケット処理ルール領域に分割し、検索結果とパケット処理ルールを同時出力する機能も内蔵した (クリックで拡大) 出典:ルネサス

左=最大検索キーを短く設定することで、検索エントリー数を200万、400万へと拡張することも可能/右=検索キーで使用する最大143ビットのビット幅を、検索キーの領域とパケット処理ルール領域に分割し、検索結果とパケット処理ルールを同時出力する機能も内蔵した (クリックで拡大) 出典:ルネサス開発サポートツールは、FPGAとLLDRAM-III間の相互運用性を検証済みのレファレンスボード、検証済みの検索IPを含むサンプルデザイン、検証環境一式、評価環境一式を用意。これにより、ユーザーは開発するネットワーク機器のハードウェアの設計と並行して、FPGA内のシステム設計と検証がスタートできる。同社によると、「同レファレンスデザインによって、約6カ月のシステム開発期間短縮に貢献する」とした。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

呉ルネサス、目指すは「W杯優勝」

呉ルネサス、目指すは「W杯優勝」

ルネサス エレクトロニクスは2016年6月28日、同日付で社長兼CEOに就任した呉文精氏の就任会見を開催し、新CEOとして、戦略的セグメントに特化するなどの経営方針、抱負を語った。 ルネサス、2020年に車載半導体シェア首位奪回へ

ルネサス、2020年に車載半導体シェア首位奪回へ

ルネサス エレクトロニクスの自動車向け事業を統括する執行役員常務の大村隆司氏は、2016年1月13〜15日に開催されている「国際カーエレクトロニクス技術展」でインタビューに応じ、2020年に世界車載半導体シェアでNXP Semiconductorsを抜き、首位に躍り出る見込みであると明かした。 2015年 車載半導体シェアランキング、首位はNXP

2015年 車載半導体シェアランキング、首位はNXP

2015年の車載半導体市場は、NXP Semiconductorsが約42億米ドルの売上高でトップに立った。2014年まで首位を維持してきたルネサス エレクトロニクスは、3位となった。 ルネサス、5年前の教訓生かした震災対策「成果出た」

ルネサス、5年前の教訓生かした震災対策「成果出た」

ルネサス エレクトロニクス社長兼CEOを務める鶴丸哲哉氏は2016年5月11日、熊本地震で被災した熊本地区製造拠点の復旧作業状況について説明を行った。