4DS Memoryが40nmプロセス適用のReRAMを開発:狙いはモバイルクラウド

オーストラリアの4DS Memoryが、40nmプロセスを適用したReRAMを開発した。モバイルクラウドの分野をターゲットとする。

40nmプロセスのReRAM

オーストラリアのウエストパース(West Perth)に拠点を置く4DS Memoryが、40nmプロセスを適用したReRAMを開発したと発表した。フラッシュメモリや、競合企業であるCrossbarのReRAMよりも、高い記憶密度を実現したという。Crossbarは最近、中国のファウンドリーであるSMICにReRAMのライセンスを供与したと報じられている。

4DS MemoryのCEO(最高経営責任者)であり、マネージングディレクターを務めるGuido Amout氏は、EE Timesのインタビューに対し、「Crossbarは、40nmプロセスの設計ルールを用いたということ以外、セル寸法などの詳細については一切明らかにしていない。このため、セルの長さ寸法に関しては、40nmの倍数であると推測するしかない。さらに重要なのが、Crossbarが、小型化の実現が困難なフィラメント型ReRAM技術を採用しているという事実だ」と述べている。

4DS Memoryは、「業界初となる40nm ReRAMを実現した」と主張しているが、これまで同社やCrossbarの他にもさまざまな研究開発企業が、ReRAM/メモリスタの開発に取り組んできた。例えば、Adesto Technologiesや旧エルピーダメモリ、パナソニック、富士通、NEC、Samsung Electronics(サムスン電子)、GLOBALFOUNDRIES、SanDisk、Rambusなどだ。この他にも、IMECがTSMCと協業したように、研究開発機関がファウンドリーパートナーと協業関係を構築する事例もいくつかある。

フラッシュメモリの微細化が間もなく限界を迎えるといわれている中、3D(3次元)構造への移行が加速している。その一例として、東芝と米Western Digital(ウエスタンデジタル)が64層の3Dフラッシュメモリ「BiCS FLASH」のサンプル出荷を開始すると発表したことなどが挙げられる*)。

*)関連記事:東芝、64層の3D NANDをサンプル出荷「世界初」

一方4DS Memoryは、HGST(旧日立グローバルストレージテクノロジーズ)との協業により、過去2年間をかけて、ReRAM技術の開発を行ってきた。HGSTは現在、Western Digitalの子会社となっている。

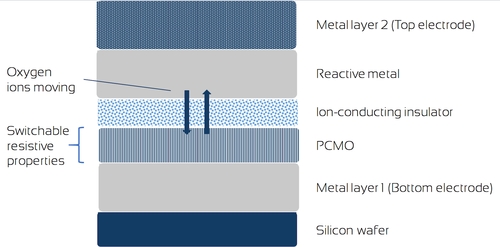

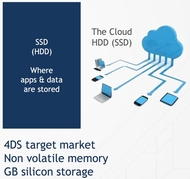

両社は協業し、ペロブスカイトと酸素イオン移動を用いた非フィラメント型技術を適用することにより、フラッシュメモリよりも高性能な「Interface Switching ReRAM」を開発した。モバイルクラウドにおいて、ギガバイトクラスのストレージ性能を経済的に実現することが可能だという。

また、4DS Memoryは2016年7月に、ReRAMの拡張性やサイクリング耐性のさらなる最適化を目指し、HGSTとの共同開発契約をもう1年延長したという。

4DS Memoryによると、同社が最近デモを披露したチップの研究開発資金は、1200万米ドル程度にとどまるという。同社は、「このデモチップにより、当社のReRAMメモリセルが、3D NANDフラッシュよりも高速化と低コスト化、低消費電力化を実現しているということを実証できた。このため、400億米ドル規模の世界フラッシュメモリ市場において、新たな市場を切り開くことができる」と述べている。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

スピン注入型MRAMの不都合な真実

スピン注入型MRAMの不都合な真実

STT-MRAMの基礎を解説するシリーズ。最終回となる今回は、磁気トンネル接合(MTJ)を構成する固定層や磁性層に焦点を当てる。スピン注入型MRAMのMTJは、47層もの層で構成されている。これほどの層が必要なのにはきちんとした理由があるのだが、実は同時にそれがSTT-MRAMの弱点にもなっている。 消費電力0.01mWの水素センサー、ReRAMがヒントに

消費電力0.01mWの水素センサー、ReRAMがヒントに

パナソニックは「CEATEC JAPAN 2016」(2016年10月4〜7日、千葉・幕張メッセ)で、現在開発中の水素検知センサーを展示した。水素検知センサーは、パナソニックが開発した新しい検出原理を採用したもので、既存品と感度は同等だが、消費電力が1万分の1以下となっている。 次世代メモリ、STT-MRAMが優勢か

次世代メモリ、STT-MRAMが優勢か

IMECは、STT-MRAM(スピン注入磁化反転型磁気メモリ)を次世代メモリの最有力候補とみているようだ。 FinFETサイズの物理的な限界は?

FinFETサイズの物理的な限界は?

ベルギーで開催された「IMEC Technology Forum(ITF) 2016」では、2.5D(2.5次元)のチップ積層技術や、FinFETのサイズの物理的な限界についても触れられた。