製造コスト「数十分の1」、卓上半導体工場:IoTからIoEへ(3/5 ページ)

半導体製造の後工程に革新が生まれそうだ。コネクテックジャパンは製造プロセスを一新することで、後工程に必要なコストを抑え、実装時間を短縮するフリップチップ実装装置「MONSTER DTF」を開発した。特徴は低荷重、低温で半導体パッケージを基板に実装すること。例えばMEMSパッケージをフリップチップ実装できるようになり、最終製品の小型・軽量化にもつながるという。

半導体製造の後工程を改善

MONSTER PAC技術を開発し、MONSTER DTF装置の公開に至った背景には、半導体産業が抱える矛盾があったのだという。

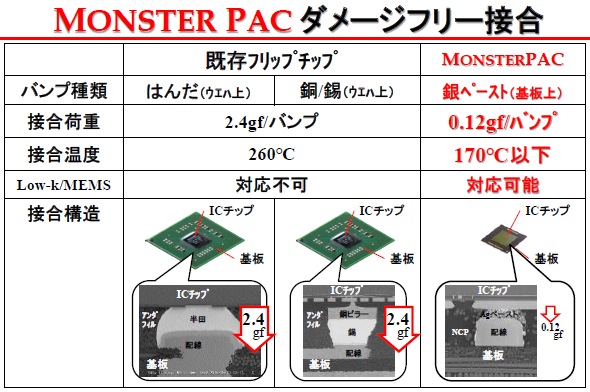

半導体パッケージを基板上に高密度実装する場合、現在標準的な手法はワイヤボンディングではなく、ワイヤを使わないフリップチップ実装だ。フリップチップ実装ではパッケージの表面にはんだ(または銅やスズ)端子を形成し、基板に載せ、高温下で高い接合荷重をかける。こうして基板上の配線と半導体パッケージの間に強固な結合を作り上げる。

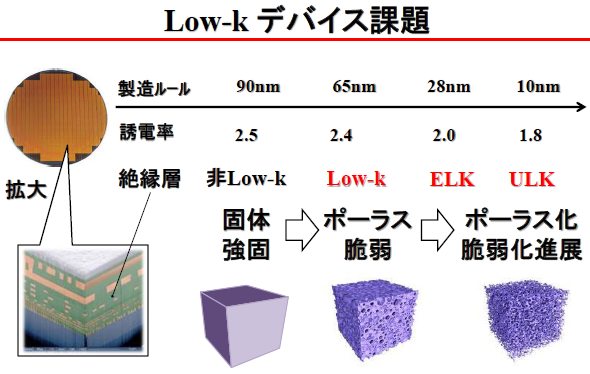

「半導体の微細化、高速処理が進むにつれて、複数の層からなる半導体の絶縁層に要求が来ることが分かっていた。信号の遅延を起こさないよう絶縁層の誘電率を低くすること(low-k化)だ。low-k化が進むと、密で強固な絶縁層ではなく、ポーラス化した脆弱な絶縁層を使わざるを得ない(図3)。こうなると、高い接合荷重が必要な従来技術では立ちゆかなくなると考えた。ところがフリップチップ実装にはこの10年間イノベーション(技術の新結合)が全く起きていない」(平田氏)

そこで同社が開発したのがMONSTER PAC技術だ。従来のはんだバンプでは、1端子(バンプ)当たり2.4gf(グラム重)の接合荷重を必要とした。「これは1mm角に3トンの力を加えることに等しい。大型の装置がこれまで必要だった理由だ。当社の技術では接合荷重を、20分の1の0.12gfに減らすことができた」(平田氏、図4)。Low-k絶縁層に害を与えないことはもちろん、後ほど登場するMEMSにも適した技術だという。

Copyright © ITmedia, Inc. All Rights Reserved.