モデルベース環境MATLAB、HDL検証も効率化する:FPGAインザループを高速化

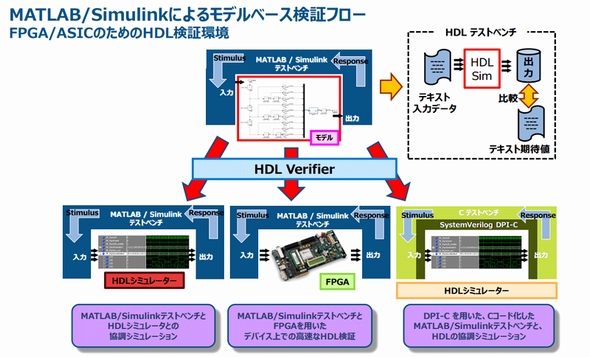

モデルベース環境「MATLAB/Simulink」を提供するThe MathWorks。同社の山口貴久氏は、「オプションの『HDL Verifier』を使用することで、HDL検証を効率化できる」と語る。

FPGAインザループを高速化

The MathWorksは、モデルベース環境「MATLAB/Simulink」におけるHDL(ハードウェア記述言語)に対応した「HDL Verifier」の新機能を2016年12月に発表した。HDL Verifierは、ハードウェアベースの検証作業を効率化するMATLAB/Simulinkのオプションを指す。新機能は、評価ボードを用いた検証「FPGAインザループ」の高速化だ。

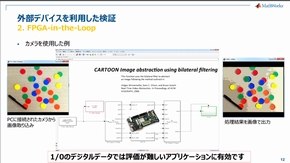

新機能では、周波数をカスタムに設定ができるようになり、従来のFPGAインザループと比較して最大5倍の速さのクロックレートで動作可能となった。XilinxとIntel FPGA(旧Altera)の開発ボードに対応。開発ボードと接続するインタフェースとしてギガビットイーサネットに加え、PCI Express(以下、PCIe)に対応。PCIeを使用したシミュレーションでは、ギガビットイーサネットと比較して3〜4倍の速度で実行できるという。

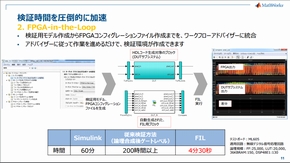

従来のシミュレーションベースで200時間以上要したHDL検証も、FPGAインザループ機能をXilinxの開発ボード「Virtex-6 FPGA ML605」と合わせて使用すれば、4分30秒で実行可能という。Simulinkのテストベンチ作成時間60分を加えても、検証時間短縮が期待できる。

また、検証用モデル作成からFPGAコンフィギュレーションファイル作成までをワークフローアドバイザー内に統合している。ワークフローアドバイザーの指示に従って作業を進めるだけで、検証環境を作成できるのも特長である。

左=検証用モデル作成からFPGAコンフィギュレーションファイル作成までをワークフローアドバイザー内に統合/右=FPGA評価ボードを利用した検証のイメージ (クリックで拡大) 出典:The MathWorks

左=検証用モデル作成からFPGAコンフィギュレーションファイル作成までをワークフローアドバイザー内に統合/右=FPGA評価ボードを利用した検証のイメージ (クリックで拡大) 出典:The MathWorks同社アプリケーションエンジニアリング部の信号処理・通信&テクニカルコンピューティング分野で部長を務める山口貴久氏は「HDLの検証結果は1、0のデータで出力される。しかし、自動車のADAS(先進運転支援システム)を中心に画像を扱う企業が増えているため、1、0のデータではなく、実際の画像を見たいというニーズが高まっている。HDL Verifierでは画像として確認、評価が可能である」と語る。

従来より8.5倍高速化する「DPI-Cテストベンチ」

山口氏はFPGAインザループの他に、HDL Verifierに関する2つの特長を挙げた。1つ目は、論理シミュレーターとの協調シミュレーションである。MATLAB/Simulinkの関数やブロックライブラリを用いることで、「HDLで記述が難しいテストベンチを直感的に記述できる」(山口氏)と語る。論理シミュレーターとのインタフェースは自動で作成でき、シミュレーション結果はMATLAB/Simulink上で解析可能だ。

2つ目は、膨大なテストデータや長時間のシミュレーションに対応する「DPI-Cテストベンチ」である。DPIとはSystemVerilogと外部言語のインタフェースであり、C言語のDPIがDPI-Cとして定義されている。SystemVerilogからCコードの関数を使用したり、CコードからSystemVerilogのタスクや関数を利用できる。

山口氏によると、DPI-CテストベンチではSimulinkモデル全体をCコード化して使用するため、C言語ベースでのテストベクタ作成も不要になる。生成時間がテストベクタのサイズに依存せず、論理シミュレーターとI/Oファイル間のやりとりがないため、シミュレーション時間の削減にもつながるという。これにより、HDL生成とテストベンチ生成、HDLシミュレーションにおけるトータル時間は「File I/Oと比較して、8.5倍高速化することができた」(山口氏)と語る。

「MATLAB/Simulinkは難しいツールと思われていることも多いが、使いやすさを意識した工夫、改善を続けている。ぜひ、HDL検証においても活用してほしい」(山口氏)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

“熱流”を手軽に計測できるロガー――日置電機

“熱流”を手軽に計測できるロガー――日置電機

日置電機は、熱エネルギーの移動を検知する熱流センサーを使用したデータロガーの提案を拡大させている。熱流センサー部をフレキシブルで小型化するとともに、センサー部とロガー部をワイヤレス接続化するなど多数の工夫を盛り込むことで、従来、建材や住宅用途に限られていた熱流計測の応用範囲を自動車や電子機器設計現場などへ広げ、熱流ロガービジネスを拡大させているという。 5Gを加速? モデルベース環境“MATLAB”の進化

5Gを加速? モデルベース環境“MATLAB”の進化

技術計算ソフトウェアツール「MATLAB/Simulink」を提供するThe MathWorks。第5世代移動通信(5G)、IoT市場が拡大する中で、同社は「信号処理・通信」向けライブラリの機能を拡張し、「ビットからアンテナまでをサポートする」という。また、コード生成まで行う「ものづくりとしてのサポート」も進めることで、5G、IoT市場に価値の提供を行っていく。 自動運転車の安全はどう認証すべきか(前編)

自動運転車の安全はどう認証すべきか(前編)

米運輸省が自動運転車政策のガイドラインをまとめた。最も大きな課題は、いかにして安全性を認証できるのかという点だ。 “技術力の積み重ね”で差別化を、OEGの評価試験

“技術力の積み重ね”で差別化を、OEGの評価試験

OKIエンジニアリング(OEG)は2015年2月、宇宙航空・産業機器向けの環境試験サービス事業を拡大するため、「西東京試験センター」を開設した。本記事は、西東京試験センターについてOEG社長の柴田康典氏に話を聞くとともに、施設の様子を写真で紹介していく。 複雑な高周波モジュールやアンテナ設計を効率化

複雑な高周波モジュールやアンテナ設計を効率化

AWR Japanは、「MWE 2016」で、RF/マイクロ波回路設計ソフトウェア「NI AWR設計環境」を用いた「マルチテクノロジーモジュールと増幅器設計」や「5G/レーダー向けフェーズドアレイアンテナ設計」などについて紹介した。 新型プローブ、これまで見えなかった信号を観測

新型プローブ、これまで見えなかった信号を観測

テクトロニクスは、光アイソレーション型差動プローブ「TIVMシリーズ」6製品の販売を始めた。新製品を用いることで、これまでコモンモードノイズに埋もれて見えなかった信号の観測が可能となる。