3Dチップ技術、データセンターへの活用を視野に:Oracleの元エンジニアが開発中

マイクロプロセッサの研究プロジェクトを中止したOracle(オラクル)。Oracleの元主席エンジニアはスタートアップを立ち上げ、データセンサー向けのチップ積層技術の開発を続けている。

チップスタック技術をデータセンター向けに展開

プロセスの微細化のスピードが鈍化する中、Oracleがマイクロプロセッサの研究プロジェクトを中止したことにより、ハイエンドのチップ設計の未来が垣間見えた。Oracleは、同プロジェクトで提案していた「Sparc CPU」に、開発中のチップ積層技術を採用することで優位性を得ようと狙っていた。だが、近年、そのような狙いは難しさを増しつつあるのが現状だ。

Oracleの研究プロジェクトを支えていた研究者は、同社が2017年初めにハードウェア部門に対して実施した人員削減計画で解雇されてしまった。だが、彼のアイデアは、とある新興のコンサルティング企業に引き継がれている。このスタートアップは、シリコンバレーのメーカーと既に協業している。

Oracleの元主席エンジニアであるDon Draper氏は、「ProPrincipia」を設立した。従業員はDrape氏を含めて3人だ。同氏は、「研究を進めれば進めるほど、これが進むべき道だという確信が強まっている」と述べる。

Draper氏は、「コンピューティングの密度はインターネットのトラフィックのようなスピードで増加するわけではない。それにもかかわらず、データセンターで分析するデータ量は急激に増加している。これを解決するにはメモリバンド幅を増やすことが必要だ。それに応えられるのが3D(3次元)スタッキング技術だと考えている」と説明する。

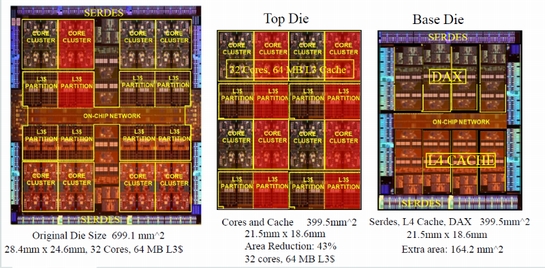

2016年下半期に開催されたあるカンファレンスでDraper氏は、Sparcプロセッサの中身を、より小さなサイズの2つのダイに分けて搭載し、それら2つのダイをスタックするという設計手法を発表した。1つのダイにはコアとキャッシュが、もう1つにSerDes、L4キャッシュ、オンチップネットワークなどの周辺回路が搭載されていて、コストと消費電力の低減を実現するという。

また、新たに登場したマイクロ流体による冷却技術を用いれば、新型チップはコアとL3キャッシュの数をほぼ倍増できる。Draper氏は「同じプロセスノードで性能を2倍にできる」と述べた。

新しいダイスタック技術は、機械学習などメモリ集約型タスク向けのアクセラレーターをホストプロセッサに接続する技術として理想的なのだという。一方で、CCIXやOpenCAPI(Coherent Accelerator Processor Interface)など、“Chip to Chip”(チップ間)のインターコネクト技術は「細長い管の上に積層するようなものだ」という。

Draper氏は、統合型電圧レギュレーター(IVR:Integrated Voltage Regulator)を用いることも提案した。比較的小型のインダクターを用いられるので消費電力と基板スペースの面積を削減できるとしている。チップの動作周波数は約150MHzまで高められるという。

【翻訳:青山麻由子、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

3次元集積化(3D IC)の理想と現実

3次元集積化(3D IC)の理想と現実

今回は、なぜシステムを複数のチップに分ける必要があるのかを説明する。後半では、パッケージに求められる目標を達成する“究極のパッケージング技術”として期待されたシリコン貫通ビア(TSV: Through Silicon Via)と、旧世代のパッケージング技術との間に存在する、大きなギャップについて解説したい。 半導体業界がポストCMOS開発に本腰

半導体業界がポストCMOS開発に本腰

2017年3月に、「CMOSトランジスタの微細化は2024年ごろに終息する」との予測が発表された。半導体業界は今、ポストCMOSの開発をより一層加速しようとしている。 2016年半導体業界の研究開発費トップ10、東芝5位

2016年半導体業界の研究開発費トップ10、東芝5位

IC Insightsは、2016年の半導体業界における研究開発費メーカー別ランキングを発表した。 SK Hynixが72層256Gb 3D NANDフラッシュを開発

SK Hynixが72層256Gb 3D NANDフラッシュを開発

SK Hynixが72層の256ビット3D(3次元)NAND型フラッシュメモリを開発したと発表した。同社は2016年から、36層128Gビット3D NANDフラッシュの発表や、48層256Gビット3D NANDフラッシュの量産開始など、3D NANDフラッシュの開発を加速している。 中国のメモリ戦略は苦難の道をたどるのか

中国のメモリ戦略は苦難の道をたどるのか

半導体技術の強化を図る中国が、メモリ産業に狙いを定めている。だがメモリは、技術開発にも製造にも膨大な資金がかかる分野だ。中国は、メモリ関連の知識と経験を持つ人材の確保に奔走しているが、「中国は苦しい選択をした」との見方を示す専門家もいる。 ルネサス、フィン構造のMONOSフラッシュを開発

ルネサス、フィン構造のMONOSフラッシュを開発

ルネサス エレクトロニクスが、フィン構造を採用したSG(Split-Gate型)-MONOSフラッシュメモリセルの開発に成功したと発表した。フィン構造としたことで、FinFETなど先端のロジックプロセスとの親和性が高くなり、次世代の16nm/14nm世代マイコンに混載できるようになる。