Hot Chips 2017、チップ積層技術に注目集まる:IntelやXilinxも独自技術を発表(2/2 ページ)

米国カリフォルニア州クパチーノで2017年8月20〜22日に開催された「Hot Chips 2017(Host Chips 29)」では、パッケージング技術やインターコネクト技術などを含め、特に2.5D(2.5次元)のチップ積層技術に注目が集まった。

2種類の「EMIB」

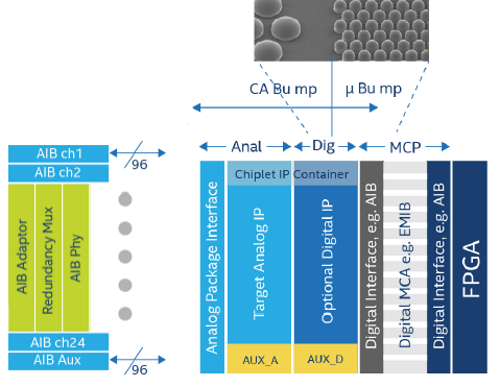

IntelはHot Chipsにおいて、2種類のEMIBインタフェースについて説明している。1つは「UIB」で、SamsungやSK Hynixが、DRAMスタック向けに実装しているJEDECリンクをベースとする。もう一方の「AIB」は、Intelがトランシーバー向けに独自開発したインタフェースで、これは後に、アナログやRFなどのさまざまなデバイスで使用できるよう汎用化されている。

Intelとしては、いずれも比較的シンプルな並列I/O回路であるため、EMIB向けシリアルリンクを使用する場合よりも、レイテンシが低く、微細化にも優れると確信しているようだ。今のところ、これらのインタフェースを使用したモジュールが、3社のファウンドリーにおいて6つの世代技術に採用されているという。

Intelは、まだAIBを正式に発表するかどうかを決めておらず、仮に発表したとしても、オープンソースにするかどうかも分からないという。AIBは、物理層において、最大2Gビット/秒(Gbps)のプログラム可能な速度で動作し、EMIBリンク上における接続数は約2万だという。

さらに、密度も向上する。次世代EMIBプロセスは、35μm径のバンプをサポートするため、既存の55μmバンプと比べると、密度を2.5倍に高められるという。

IntelのFPGAグループでシニアアーキテクトを務めるSergey Shuarayev氏は、「EMIBを使用すれば、FPGAをCPUやデータコンバーター、光学部品などに接続することが可能だ。さらに、複雑なアナログブロックをFPGAから除外することもできるため、2.5D積層技術に比べてコストを低減でき、生産量も増やせる」と述べる。

Xilinxは、Hot Chipsにおいて、最大3個の16nm FPGAと2個のDRAMをスタック可能な第4世代の積層技術「VU3xP」を発表した。2018年4月までにはサンプル出荷を開始する予定だという。ホストプロセッサやアクセラレーターに対して4つのコヒーレントリンクをサポート可能なCCIXインタフェースを使用したチップとなる。

PCIe(PCI Express)ベースのCCIXは最初に、25Gbpsで動作する。Xilinxのバイスプレジデントを務めるGaurav Singh氏は、「現在、複数のプロセッサの設計において採用されている」と述べる。

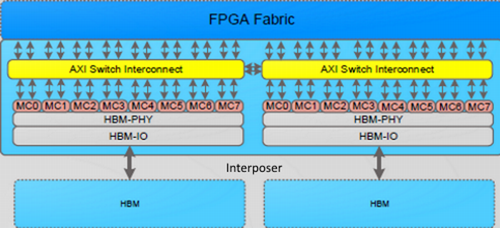

またXilinxは、メモリコントローラーアレイに伝送するためのAXIスイッチを使ったDRAM向けに独自のリンクを開発中だ。

【翻訳:田中留美、滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

モバイル端末向けパッケージング技術「FOWLP」(前編)

モバイル端末向けパッケージング技術「FOWLP」(前編)

ウエハーレベルのファンアウトパッケージング技術「FOWLP(Fan Out Wafer Level Packaging)」の製造工程は、開発企業によって大きく異なる。そこで、いくつかに大別される製造工程の違いを紹介する。 TSMCの高性能・高密度パッケージング技術「CoWoS」(前編)

TSMCの高性能・高密度パッケージング技術「CoWoS」(前編)

今回から前後編に分けて「CoWoS(Chip on Wafer on Substrate)」を解説する。CoWoSの最大の特長はシリコンインターポーザを導入したことだが、では、なぜシリコンインターポーザが優れているのだろうか。シリコンインターポーザに至るまでの課題と併せて説明する。 FPGA大手で唯一生き残るXilinx、国内戦略を聞く

FPGA大手で唯一生き残るXilinx、国内戦略を聞く

FPGA大手ベンダーで唯一買収されずに生き残っているXilinx。同社日本法人のザイリンクス社長で韓国のVice Presidentを務めるSam Rogan(サム・ローガン)氏に国内の戦略を聞いた。 自動運転でFPGAの期待値高まる、ザイリンクスがデモ

自動運転でFPGAの期待値高まる、ザイリンクスがデモ

ザイリンクスは、「第9回 国際カーエレクトロニクス技術展」(2017年1月18〜20日、東京ビッグサイト)で、ディープラーニングを使った歩行者認識、IRカメラによるドライバーモニタリングシステム、Ethernet AVBを使った高速伝送のカメラシステムなど、ADAS(先進運転支援システム)や自動運転向け技術をデモ展示した。 2017年Q2の半導体売上高、SamsungがIntelを抜く

2017年Q2の半導体売上高、SamsungがIntelを抜く

2017年第2四半期の半導体売上高において、Samsung ElectronicsがIntelを抜いた。メモリ市場が好調だったことが主な要因だ。 主流になり得た技術、わずかな開発の遅れが命取りに

主流になり得た技術、わずかな開発の遅れが命取りに

分野によっては、技術が確立されるには、長い年月が必要になる。その一方で、わずかな開発の遅れが命取りとなり、ビジネスのチャンスを逃してしまうケースがあるのもまた、事実なのである。